# Commercialization of CIS-Based Thin-Film PV

Final Technical Report August 1998 – November 2001

D.E. Tarrant and R.R. Gay Siemens Solar Industries Camarillo, California

1617 Cole Boulevard Golden, Colorado 80401-3393

NREL is a U.S. Department of Energy Laboratory

Operated by Midwest Research Institute • Battelle • Bechtel

Contract No. DE-AC36-99-GO10337

# Commercialization of CIS-Based Thin-Film PV

Final Technical Report August 1998 – November 2001

D.E. Tarrant and R.R. Gay Siemens Solar Industries Camarillo, California

NREL Technical Monitor: H.S. Ullal

Prepared under Subcontract No. ZAK-8-17619-19

1617 Cole Boulevard Golden, Colorado 80401-3393

NREL is a U.S. Department of Energy Laboratory Operated by Midwest Research Institute • Battelle • Bechtel

Contract No. DE-AC36-99-GO10337

#### **NOTICE**

This report was prepared as an account of work sponsored by an agency of the United States government. Neither the United States government nor any agency thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States government or any agency thereof.

Available electronically at http://www.osti.gov/bridge

Available for a processing fee to U.S. Department of Energy and its contractors, in paper, from:

U.S. Department of Energy Office of Scientific and Technical Information P.O. Box 62 Oak Ridge, TN 37831-0062 phone: 865.576.8401 fax: 865.576.5728

email: reports@adonis.osti.gov

Available for sale to the public, in paper, from:

U.S. Department of Commerce National Technical Information Service 5285 Port Royal Road Springfield, VA 22161

phone: 800.553.6847 fax: 703.605.6900

email: orders@ntis.fedworld.gov

online ordering: <a href="http://www.ntis.gov/ordering.htm">http://www.ntis.gov/ordering.htm</a>

# **Preface**

Siemens Solar Industries (SSI) has pursued the research and development of CuInSe<sub>2</sub>-based thin film PV technology since 1980 [1]. At the start of subcontract activities with NREL, SSI had demonstrated a 14.1% efficient 3.4 cm<sup>2</sup> active-area cell, unencapsulated integrated modules with aperture efficiencies of 11.2% on 940 cm<sup>2</sup> and 9.1% on 3900 cm<sup>2</sup>, and an encapsulated module with 8.7% efficiency on 3883 cm<sup>2</sup> (verified by NREL).

SSI began a 3-year, 3 phase cost-shared subcontract (No. ZN-1-19019-5) on May 1, 1991 with the overall project goal of fabricating a large area, stable, 12.5% aperture efficient encapsulated CIS module by scaleable, low-cost techniques on inexpensive substrates. Subcontract accomplishments were facilitated by addressing module reproducibility using small area test devices and mini-modules. Statistical process control disciplines were adopted to rigorously quantify process reproducibility. SSI addressed uniformity and reproducibility of absorber formation, interactions of the substrate with the absorber, and performance losses near interconnects. Subcontract accomplishments included demonstration of encapsulated module efficiencies that were at that time the highest reported mini-module efficiencies for any thin film technology (encapsulated 12.8% efficient mini-module on 68.9 cm<sup>2</sup> and an NREL-verified 12.7% efficient unencapsulated circuit on 69 cm<sup>2</sup> with a prismatic cover), demonstration of a champion large area (3860 cm<sup>2</sup>) encapsulated module efficiency of 10.3% (verified by NREL) that was the first thin film module of its size to exceed the 10% efficiency level, and delivery to NREL of a one kilowatt array of large area (~3890 cm<sup>2</sup>) approximately 30 watt modules [2].

From September 1995 through December 1998, SSI participated in a 3-year, 3 phase cost-shared TFPPP subcontract (No. ZAF-5-14142-03). The primary objective of this subcontract was to establish reliable high-throughput, high-yield thin film deposition processes in order to make CIS a viable option for the next generation of photovoltaics. Outdoor testing, accelerated environmental testing, and packaging development progressed throughout all phases of this subcontract. During Phase 1, SSI rigorously demonstrating process reproducibility and yield for a 10x10-cm monolithically interconnected "mini-module" baseline process and demonstrated a 13.6% aperture area efficient mini-module (verified by NREL). During Phase 2, SSI demonstrated the need to replace an existing large area reactor with a reactor based on a more direct scale-up of the baseline reactor, built a new large area reactor, and demonstrated comparable performance for the mini-modules baseline and 28x30-cm circuit plates. developed products and prototype large area modules using a new package designed to integrate small circuit plates into larger modules. A one kilowatt array of Cu(In,Ga)(S,Se)2 modules was delivered to NREL replacing a previously installed array based on an older absorber formation technology without sulfur incorporated in the absorber (Cu(In,Ga)Se<sub>2</sub>). This array demonstrated significant improvements in efficiency and the temperature coefficient for power. introduced two new 5-watt (ST5) and 10-watt (ST10) CIS-based products designed for use in 12 V systems, and NREL confirmed a new world-record efficiency of 11.1% on a SSI large area (3665 cm<sup>2</sup>) module. During subcontract Phase 3, substrate size was scaled from ~30x30 cm to ~30x120 cm and good process control was demonstrated with an average efficiency of 10.8%. Commercial product samples were delivered to NREL and a second set of ~30x120 cm modules (32 modules totaling ~1.2 kW) was delivered to the NREL Outdoor Test Facility. The NREL

measured average efficiency at standard test conditions of 11.4% was at that time the highest large area efficiency for any thin-film technology and NREL confirmed a world-record 11.8% large area (3651 cm<sup>2</sup>) efficiency for the champion module [3].

The primary objectives of this subcontract are to scale up substrate size and to scale up production capacity of the baseline SSI CIS-based module process while introducing CIS-based products. The primary goals of this subcontract are to scale the substrate size from approximately 900 cm² (1 ft²) to approximately 4000 cm² by the middle of the Phase II, and to achieve pilot production rates of 500 kW per year by the end of Phase III. Deliverables for the subcontract include CIS-based products and representative modules delivered to the NREL Module Testing Team for outdoor testing and evaluation. SSI will continue mid-term and longer-term thin-film R&D with the goals of:

- Assuring future product competitiveness

- Improving module performance

- Reducing cost per watt

- Assuring product reliability

This document reports on progress toward these objectives and goals through this three-year subcontract (August 1998 through November 2001).

# **Acknowledgments**

Siemens Solar Industries wishes to acknowledge the contributions of the following people and organizations.

The Siemens Solar Industries CIS Team:

M. Dietrich

O. Frausto

C. Rischmiller

R. Gay (Program Manager)

D. Heinemann

J. Henderson

C. Köble

D. Tarrant (Principal Investigator)

J. Waher

S. Voss

J. MaherS. VossP. NorumR. WietingH. NguyenD. Willett

Brookhaven National Laboratory

Colorado State University

Florida Solar Energy Center

Fraunhofer Institute / GSF

Institute of Energy Conversion / University of Delaware

National Renewable Energy Laboratory

Pennsylvania State University

Showa Shell Seikyu, K.K.

Siemens Solar GmbH

Siemens AG

Washington State University

# **Summary**

Compared to traditional wafer-based crystalline silicon technologies, monolithic integration of thin film solar cells can lead to products of comparable performance but with significant manufacturing advantages [1]: lower consumption of direct and indirect materials, fewer processing steps and easier automation. Monolithic integration is required to achieve these advantages since this eliminates multiple process steps and handling operations during formation of the absorber and during module assembly. The basic module elements for all thin-film technologies (alloys of amorphous silicon, cadmium telluride and CIS) are the same; the module elements are a circuit-glass/cover-glass laminate, a frame, and a junction box. The basic circuit elements are also very similar; they each have a base electrode, an absorber, a junction, a top electrode and three patterning steps for monolithic integration. While the details of these module elements or equivalent module elements differ, the basic cost structures are very similar on an area-related basis. Since the cost per unit area is the same, the cost per watt is inversely proportional to the module efficiency. CIS cells and monolithically integrated modules have demonstrated the highest efficiencies of any candidate thin-film technologies; therefore, CIS is expected to have the lowest manufacturing cost/watt.

The primary objectives of the SSI "Commercialization of CIS-Based Thin-Film PV" subcontract were to scale-up substrate size and to increase production capacity of the baseline CIS module process while introducing CIS-based products. An additional mid- to longer-term objective was to advance CIS based thin-film technology thereby assuring future product competitiveness by improving module performance, cost per watt produced, and reliability. The foundation of SSI's approach to process scale-up, process optimization, and demonstration of product durability was the application of design of experiment and statistical process control methodologies. These combined objectives were pursued to fabricate efficient and stable thin-film modules made by scaleable, manufacturable, low-cost techniques. SSI milestones for this subcontract were to:

- Scale from a substrate size of approximately 900 cm<sup>2</sup> to a substrate size of approximately 4000 cm<sup>2</sup> (4 ft<sup>2</sup>) by the middle of the second phase of this subcontract. The criteria for achievement of this milestone was a 4000 cm<sup>2</sup> circuit plate process that had been adopted for SSI commercial activities and was reproducible as determined by statistical process control criteria.

- Achieve a pilot production rate 500 kW per year by the end of subcontract

During this subcontract, SSI applied systematic research, development, production and business methodologies to a carefully planned substrate size and capacity scale-up of CIS-based thin-film technology. These methodologies included Statistical Process Control (SPC), Analysis of Variation (ANOVA), and Design of Experiments (DOE) --- approaches widely recognized as appropriate for manufacturing businesses. SSI also conducted research and development on longer-term issues in support of SSI's ongoing commitment to improve this technology. SSI independently and in conjunction with TFPPP team activities pursued improved understanding of processes, devices, and materials. SSI's role in advancing mid- to longer-term CIS technology emphasizes issues related to commercialization of CIS technology and assured future product competitiveness.

Siemens Solar was the first company in the world to start production of PV modules based on CIS thin-film technology; 5-Watt and 10-Watt modules in 1998. This was a major milestone in the development of PV and, during this subcontract, R&D Magazine recognized the significance of this event by awarding the prestigious R&D 100 Award to the Siemens Solar family of CIS solar modules. NREL, the California Energy Commission and SSI shared this award.

Deliverables for the first subcontract phase were defined as 900-cm<sup>2</sup> (~1-ft<sup>2</sup>) CIS-based commercial modules with AM 1.5 aperture-area efficiency of 10%. The 10-Watt "ST10" module most closely matched this definition. However, activities during the first subcontract period led to the availability of larger commercial products with higher efficiencies than anticipated at the time the deliverables were defined. SSI expanded the CIS product line in 1999 to include 20-Watt "ST20" modules and 40-Watt "ST40" modules. Samples of these commercial products were delivered to NREL during the first subcontract phase. Also during the first subcontract phase, a record-breaking efficiency of more than 12% was verified by NREL for an ST-40 module. This result in 1999 far surpassed the DOE year 2000 goal for a commercial CIS module above 10%.

During the second subcontract phase, SSI delivered 20 ST-40 large area modules, all with efficiencies over 11%, to meet the subcontract deliverables defined as large area modules with efficiencies of over 10%. Also during this subcontract period, the average efficiency based on a Gaussian fit to the main portion of the circuit plate efficiency distribution was increased from 10.8% prior to this subcontract to 11.6% for this subcontract period. This improvement was particularly notable since it was achieved along with an over 300% increase in production volume.

No one major process improvement was responsible for this demonstrated increase in average efficiency accomplished while simultaneously increasing production volume. Instead, these advancements were due to continuous improvement of all process along with particular attention to process research for two critical processes – CIS formation in new large area reactors and the quality of molybdenum deposited in new high capacity sputtering equipment. Judicious application of manufacturing engineering disciplines (statistical process control, analysis of variation and design of experiments) led to a clear definition of near term yield issues. Process development improved adhesion, decreased breakage, addressed control of raw materials, and decreased failures associated with patterning.

Further R&D of all CIS processes for part size and capacity scale-up was pursued during the third and final subcontract phase. Major accomplishments during the third subcontract phase included addressing process issues for implementation of high quality high throughput Mo deposition and patterning, high throughput precursor deposition, and higher throughput reaction of the precursor. Circuit plate production capacity was increased by more than an order of magnitude from the beginning of this subcontract while circuit and module efficiencies were steadily improved. The second subcontract milestone – to achieve a pilot production rate 500 kW per year by the end of subcontract - was first achieved in March of 2001 and the SSI production rate has consistently exceeded this rate since June of 2001.

Demonstrated mechanical and electrical yield enhancements for baseline processing are as important as progress in circuit plate or laminate efficiency. Overall line yield losses have

typically been dominated by mechanical yield. Even so, circuit electrical yield was improved from about 90% to typically above 95% while increasing capacity! During a timeframe representative of the first phase of this subcontract (May through September 1999), overall line yield analyzed on a monthly basis ranged from 32% to 61%. During a timeframe representative of the last phase of this subcontract (January through November 2001), overall line yield ranged from 56% to 89%. This dramatic improvement through the subcontract in both the value and range of monthly yield was the result of addressing disparate special causes. The SSI CIS production process has exhibited good process control for extended periods. Improving yield has been demonstrated even while implementing new equipment, implementing process changes for increased throughput and exploring process changes for improved performance.

These significant subcontract achievements through all subcontract phases were realized by applying systematic research and development methodologies to characterize and improve SSI's CIS process. Subcontract work demonstrated both a viable process for further scale-up and the potential for further performance and yield improvements. Special causes that are inherently encountered as a process evolves were and will continue to be addressed. Progress through multiple cycles of learning has and will continue to be the way to characterize and improve processes for better production compatibility, for improved performance, to scale-up substrate size and for increased throughput.

SSI capabilities were leveraged as a Technology Partner participating in NREL team oriented TFPPP activities to address near-term to longer-term R&D topics. SSI's participation in Team activities focused primarily on understanding the fundamental mechanisms responsible for transient effects in CIGS-based devices with the objective of eliminating or minimizing their impact. SSI received support from NREL for a broad range of research topics including process development and specialty device and materials measurements. Team activities emphasized research topics common to multiple CIS R&D groups whereas additional collaborations addressed issues that were generally more specific to SSI activities. Both types of collaborations with NREL have greatly contributed to SSI's progress.

NREL also supports SSI through long term testing of arrays and individual modules at the NREL Outdoor Test Facility (OTF). Long-term outdoor stability has been demonstrated at NREL where  $\sim 30 \times 30$  cm and  $\sim 30 \times 120$  cm modules have undergone testing for over thirteen years. During this subcontract FM and UL approval was obtained for the ST series of products. The performance of the ST family of CIS thin-film products is backed by a 10-year warrantee.

Outstanding progress has been made in the initial commercialization of high performance thin film CIS technology. SSI achieved all subcontract milestones. The prerequisites for scale up of present processes have been demonstrated. Further device and production R&D can lead to higher efficiencies, lower cost, and even longer product lifetime. Remaining R&D challenges are to scale the processes to even larger areas, to reach higher production capacity, to demonstrate in-service durability over even longer times, and to advance the fundamental understanding of CIS-based materials and devices with the goal of further efficiency improvements for future products. SSI's thin-film CIS technology is poised to make very significant contributions to DOE/NREL/NCPV long-term goals - higher volume, lower cost commercial products.

# **Table of Contents**

| PREFACE                                 | I   |

|-----------------------------------------|-----|

| ACKNOWLEDGMENTS                         | III |

| SUMMARY                                 | V   |

| TABLE OF CONTENTS                       | IX  |

| LIST OF FIGURES                         | x   |

| LIST OF TABLES                          | XII |

| INTRODUCTION                            | 1   |

| Overview                                | 1   |

| SSI CIS Process                         | 2   |

| SSI's R&D Approach                      | 5   |

| Subcontract Activities and Milestones   | 5   |

| Milestones                              | 6   |

| Deliverables                            | 6   |

| TECHNICAL REVIEW                        | 7   |

| Large Area Circuit Fabrication          | 7   |

| Circuit Plate & Module Statistics       | 7   |

| Process Development Examples            | 14  |

| Module Packaging and Product Durability | 28  |

| National CIS R&D Team Participation     | 35  |

| Milestones and Deliverables             | 41  |

| Milestones                              | 41  |

| Deliverables                            | 43  |

| CONCLUSIONS                             | 47  |

| REFERENCES                              | 49  |

# **List of Figures**

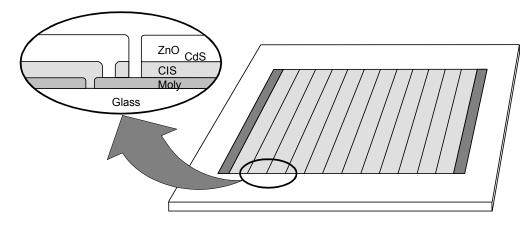

| Figure 1. Structure of SSI's monolithically integrated thin-film circuits                         | 1  |

|---------------------------------------------------------------------------------------------------|----|

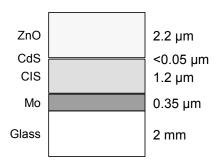

| Figure 2. Structure of SSI's CIS cell structure (not to scale)                                    | 3  |

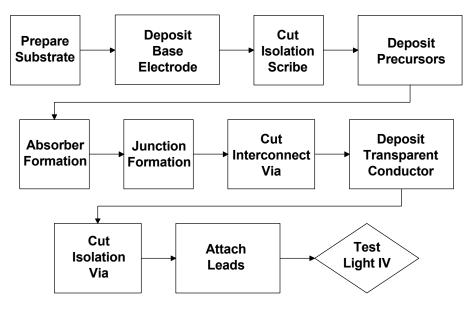

| Figure 3. SSI CIS Circuit Processing Sequence.                                                    | 3  |

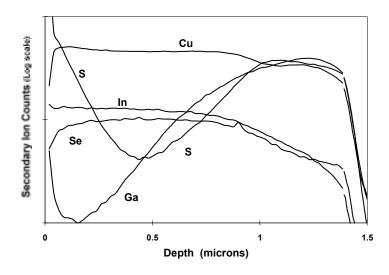

| Figure 4. Typical elemental profile for the SSI graded absorber (SIMS from NREL).                 | 4  |

| Figure 5. Single circuit plate module configuration with a TPAT backsheet                         | 4  |

| Figure 6. CIS Circuits Produced January through November 1998                                     | 7  |

| Figure 7. CIS Circuit Efficiency Distribution - January through November 1998                     | 8  |

| Figure 8. CIS Circuits Produced October 1998 through September 1999                               | 9  |

| Figure 9. CIS Circuit Efficiency Distribution - October 1998 through September 1999               | 9  |

| Figure 10. CIS Circuit Efficiency Distribution - September 1999 through August 2000               | 10 |

| Figure 11. Module production distribution - September 1999 through August 2000                    | 11 |

| Figure 12. Module production distribution - January through September 2001                        | 11 |

| Figure 13. Dependence of Voc on reactor position                                                  | 15 |

| Figure 14. Dependence of bandgap on reactor position.                                             | 16 |

| Figure 15. Lack of correlation between Voc and local temperature within the reactor               | 16 |

| Figure 16. The dependence of Mo scribe appearance on background ${\rm O_2}$ during Mo deposition  | 18 |

| Figure 17. Diagrammatic representation of the effect of an individual laser pulse                 | 18 |

| Figure 18. Relative dimensions of the affected Mo region versus normalized laser beam dimensions. | 19 |

| Figure 19. Laser scribes for Mo deposition conditions leading to poor and high quality P1 scribes | 20 |

| Figure 20. NREL supplied SEM of an etched P1 isolation via                                        | 21 |

| Figure 21. Module performance for laser and etched Mo patterning                                  | 22 |

| Figure 22. Optical micrograph of a patterned and scratched area analyzed by NREL                  | 23 |

| Figure 23. Indium sputter rate drift.                                                             | 24 |

| Figure 24. New high throughput base electrode and precursor sputtering equipment                  | 25 |

| Figure 25. Precursor morphology dependence on sputtering conditions                               | 25 |

| Figure 26. | Nearly identical elemental profiles for two samples from two sputtering systems                                                | 26 |

|------------|--------------------------------------------------------------------------------------------------------------------------------|----|

|            | Circuit plate and laminate performance for ZnO doping relative seline conditions                                               | 27 |

| Figure 28. | NREL OTF long term outdoor stability measurements - pulsed solar simulator                                                     | 28 |

| Figure 29. | NREL OTF long term outdoor stability measurements - outdoors measurements                                                      | 29 |

|            | Temperature corrected power vs. time for the third 1kW array ered to the NREL OTF in 1998.                                     | 30 |

|            | SSI analysis of OTF data for temperature corrected power vs.  n date for the third 1kW array delivered to the NREL OTF in 1998 | 30 |

|            | Comparison of present module encapsulation with Glass/Glass sulation options including thin film edge deletion.                | 31 |

| Figure 33. | Test fixture etching based edge deletion.                                                                                      | 33 |

| Figure 34. | Circuit plate with successful etch based edge deletion                                                                         | 33 |

| Figure 35. | EDS spectra for a laser edge deleted section of a module.                                                                      | 34 |

| Figure 36. | NREL/SSI buffer and window layer comparisons                                                                                   | 36 |

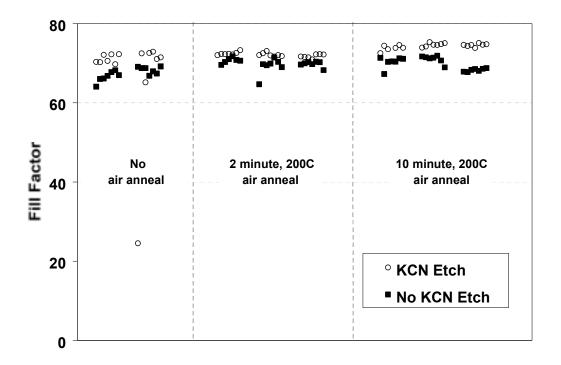

| Figure 37. | FF for mini-modules after a thermal stress                                                                                     | 39 |

| Figure 38. | Data from SSI/NREL collaborations related to buffer layers                                                                     | 40 |

| Figure 39. | SSI's CIS thin-film module products                                                                                            | 42 |

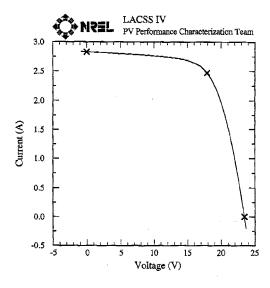

| Figure 40. | World-record 12.1 percent conversion efficiency large area CIS module                                                          | 42 |

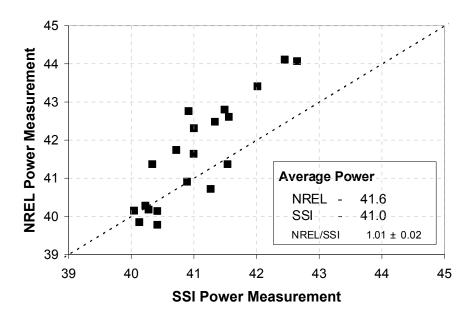

| Figure 41. | Correspondence between NREL and SSI measurements for deliverables                                                              | 44 |

# **List of Tables**

| Table 1. | Circuit production capacity and efficiency progress.                                 | . 12 |

|----------|--------------------------------------------------------------------------------------|------|

| Table 2. | Yield data for two timeframes representative of the end of this subcontract          | . 13 |

| Table 3. | XPS analysis of an etched Mo isolation scribe (percent concentration)                | . 22 |

| Table 4. | Circuit performance versus absorber thickness                                        | . 26 |

| Table 5. | Statistical analysis of SSI circuit plates (two minutes measurements) and NREL cells | . 38 |

| Table 6. | NREL measurements of at 20 ST5 modules.                                              | . 45 |

## Introduction

#### Overview

Multinary Cu(In,Ga)(Se,S)<sub>2</sub> absorbers (CIS-based absorbers) are promising candidates for reducing the cost of photovoltaics well below the cost of crystalline silicon. CIS champion solar cells have exceeded 18% efficiency for devices fabricated at NREL [4]. Small area, fully integrated modules exceeding 13% in efficiency have been demonstrated by several groups [5]. During this subcontract (1999) a record breaking efficiency of more than 12% for a commercial large area module was verified by NREL [6] exceeding DOE year 2000 goal for a commercial CIS module above 10%.

Long-term outdoor stability has been demonstrated at NREL by ~30x30 cm and ~30x120 cm SSI modules which have been in field-testing for over thirteen years. Projections based on current processing indicate production costs well below the cost of crystalline silicon [5].

Compared to traditional wafer-based crystalline silicon technologies, new thin film technologies yield products of comparable performance but with significant advantages in manufacturing [5, 7]:

- Lower consumption of direct and indirect materials

- Fewer processing steps

- Easier automation

Lower consumption of direct and indirect materials results in part from the thin-film structure for the semiconductor used to collect solar energy. All three of these manufacturing advantages are in part due to an integrated, monolithic circuit design illustrated in Figure 1. Monolithic integration eliminates multiple process steps that are otherwise required to handle individual wafers and assemble individual solar cells into the final product.

Figure 1. Structure of SSI's monolithically integrated thin-film circuits.

A number of thin film photovoltaic technologies have been developed as alternatives to the traditional solar cells based on crystalline silicon wafers [5]. The technologies with the greatest potential to significantly reduce manufacturing costs are based on alloys of amorphous silicon (a-Si), cadmium telluride (CdTe), CIS, and film silicon (Si-film). These photovoltaic thin film technologies have similar manufacturing costs per unit area since all share common elements of design and construction:

- Deposition of typically three layers on a suitable substrate window/electrode, absorber, and back electrode

- Patterning to create monolithically integrated circuit plates

- Encapsulation to construct modules

Cost per watt is a more appropriate figure of merit than cost per unit area [5]. All thin film technologies have similar manufacturing costs per unit area since they all use similar or equivalent deposition, patterning, and encapsulation processes. About half of the total module cost – material, labor, and overhead – originates in the encapsulation scheme which is for the most part independent of the thin film technology. Costs for alternative encapsulation schemes are typically similar or even higher. The average efficiency of large, ~30x120 cm modules in pilot production at Siemens Solar is approximately 11%. This performance is comparable to many modules based on crystalline silicon, and is substantially better than the performance reported for competing thin-film technologies. The lowest cost per peak watt will result from the technology with the highest efficiency, CIS technology, since most thin film technologies have similar cost per unit area.

#### **SSI CIS Process**

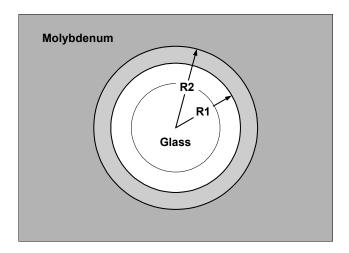

Most terrestrial photovoltaic products today are designed to charge a 12-volt battery, however the output voltage of an individual solar cell is typically about 0.5 volts. Wafer-based technologies build up the voltage by connecting individual solar cells in series. In contrast, CIS circuits are fabricated monolithically (Figure 1); the interconnection is accomplished as part of the processing sequence to form the solar cell by alternately depositing a layer in the cell structure and patterning the layer using laser or mechanical scribing.

The structure of a SSI CIS solar cell is shown in Figure 2. The full process to form CIS circuit plates, including monolithic integration, is outlined in Figure 3. This process starts with ordinary sodalime window glass, which is cleaned and an SiO<sub>2</sub> barrier layer is deposited to control sodium diffusion and improve adhesion between the CIS and the molybdenum (Mo) base electrode. The Mo base electrode is sputtered onto the substrate. This is followed by the first patterning step (referred to as "P1") required to create monolithically integrated circuit plates – laser scribing to cut an isolation scribe in the Mo electrode. Copper, gallium and indium precursors to CIS formation are then deposited by sputtering. Deposition of the precursors occurs sequentially from two targets in an in-line sputtering system, first from a copper-gallium alloy target (17 at% Ga) and then from a pure indium target. CIS formation is accomplished by heating the precursors in H<sub>2</sub>Se and H<sub>2</sub>S to form the CIS absorber. Beginning at room temperature, furnace temperature is ramped to around 400°C for selenization via H<sub>2</sub>Se, and ramped again to around 500°C for subsequent sulfidation via H<sub>2</sub>S, followed by cool-down to room temperature. This deposition of copper and indium precursors followed by reaction to form CIS is often referred to

as the two-stage process. A very thin coating of cadmium sulfide (CdS) is deposited by chemical bath deposition (CBD). This layer is often referred to as a "buffer" layer. A second patterning step (P2) is performed by mechanical scribing through the CIS absorber to the Mo substrate thereby forming an interconnect via. A transparent contact is made by chemical vapor deposition (CVD) of zinc oxide (ZnO). This layer is often referred to as a "window layer" or a transparent conducting oxide (TCO). Simultaneously, ZnO is deposited on the exposed part of the Mo substrate in the interconnect via and thereby connects the Mo and ZnO electrodes of adjacent cells. A third and final patterning step (P3) is performed by mechanical scribing through the ZnO and CIS absorber to isolate adjacent cells.

Figure 2. Structure of SSI's CIS cell structure (not to scale).

Figure 3. SSI CIS Circuit Processing Sequence.

The CIS-based absorber referred to in this report is composed of the ternary compound CuInSe<sub>2</sub> combined with sulfur and gallium to form the multinary compound Cu(In,Ga)(S,Se)<sub>2</sub>. Gallium and sulfur are not uniformly distributed throughout the absorber but the concentrations are graded; hence, this structure is referred to as a "graded absorber." The graded absorber structure is a graded Cu(In,Ga)(Se,S)<sub>2</sub> multinary with higher sulfur concentration at the front and back and higher Ga concentration at the back. Elemental profiles typical of the SSI graded absorber structures are presented in Figure 4. Efficiency, voltage, and adhesion improvements have been reported for the SSI graded absorber structure [2, 8, 9].

Figure 4. Typical elemental profile for the SSI graded absorber (SIMS from NREL).

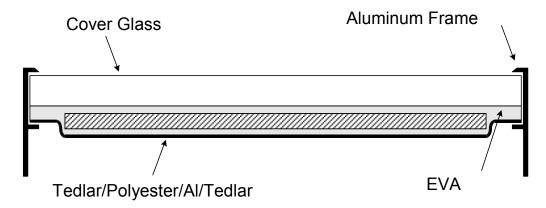

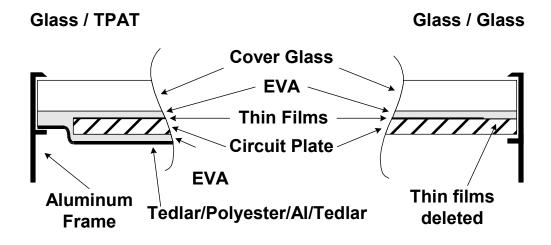

Figure 5 illustrates the module configuration used for prototypes and ST products during this subcontract period [3]. EVA is used to laminate circuit plates to a tempered cover glass and a Tedlar/polyester/Al/Tedlar (TPAT) backsheet provides a hermetic seal. Aluminum extrusions are used to build frames for the modules. In addition to providing a hermetic seal, the combination of the TPAT backsheet and the offset between the circuit plate and the frame provides electrical isolation from the frame.

Figure 5. Single circuit plate module configuration with a TPAT backsheet.

# SSI's R&D Approach

From the industrial perspective, the full process sequence anticipated for use in large-scale production must be mastered and rigorously demonstrated. The SSI research approach is composed of two main elements:

- Experimentation and development using device structures that exercise all aspects of large area module production [10]

- Application of statistical process control (SPC) as the discipline to rigorously quantify process reproducibility, and application of statistical methods such as analysis of variation (ANOVA) to rigorously quantify experimental results [11, 12].

Process predictability is a prerequisite for commercialization of thin-film PV since product performance ratings, yields and costs must be known before committing to produce products. Also, process predictability is essential for proper interpretation of process development efforts since experimental results may be ambiguous or misleading if compared to an unpredictable baseline process. SSI has adopted SPC methodologies because SPC was developed to rigorously quantify process reproducibility and process capability; the essence of SPC is predictability. Equally significantly, SPC provides the measure of systematic progress as processes are developed. Communication of this progress is typically best expressed in the language of the SPC discipline [13]. For example, process characterization results are demonstrated to be "statistically significant" based on knowledge of process repeatability measured using the SPC discipline and compared to a predictable baseline process. Confidence in the appropriate interpretation of experimental results is gained through application of statistical methods such as ANOVA to demonstrate statistically significant results.

#### **Subcontract Activities and Milestones**

The primary work of this subcontract is to advance module fabrication processes by progressively scaling substrate size and capacity for the SSI baseline CIS circuit-plate process. Simultaneously, SSI is pursuing understanding of the impact of circuit plate and module fabrication processes on device performance and module reliability. Understanding and optimization of the these processes is based on the application of DOE and SPC methodologies to identify dominant process issues and address process specific topics. Five subcontract activities have been defined to support this work:

**Substrate Size Scale-up** – The primary emphasis for this activity is to progressively scale substrate size from approximately 900 cm<sup>2</sup> (1 ft<sup>2</sup>) approximately 4000 cm<sup>2</sup> (4 ft<sup>2</sup>).

**Capacity Scale-up** - The technical base supporting manufacturability will be advanced as the production capacity is increased to about 500 kW/yr.

**Product Durability** - SSI will continue package development and qualification in parallel with substrate size and capacity scale up.

Environment, Safety and Health (ES&H) - SSI will continue internal programs and collaborative efforts such as with the TFPPP ES&H team to safely produce CIS-based

devices and modules and to explore technical approaches for removing and recycling module components.

**Process Improvements** – This task emphasizes advancement of the technical base supporting manufacturing as SSI scales up substrate size and capacity. SSI capabilities are leveraged as a Technology Partner participating in NREL team oriented TFPPP activities to address near-term to longer-term R&D topics.

### **Milestones**

SSI milestones for this subcontract are to:

- Scale from a substrate size of approximately 900 cm<sup>2</sup> to a substrate size of approximately 4000 cm<sup>2</sup> (4 ft<sup>2</sup>) by the middle of the second phase of this subcontract. The criteria for achievement of this milestone is a 4000 cm<sup>2</sup> circuit plate process that has been adopted for SSI commercial activities and is reproducible as determined by statistical process control criteria.

- Achieve a pilot production rate of 500 kW per year by the end of this subcontract

### **Deliverables**

The following deliverables have been defined for each phase of this subcontract.

#### Phase I

- D1. End of the 12th month: Deliver ten (10) 900-cm<sup>2</sup> (1-ft<sup>2</sup>) CIS-based commercial modules with AM 1.5 aperture-area efficiency of 10%.

- D2. End of the 12th month: Deliver ten (10) 900-cm<sup>2</sup> (1-ft<sup>2</sup>) CIS-based commercial modules with AM 1.5 aperture-area efficiency of 10% for the NREL Module Testing Team.

#### Phase II

- D3. End of the 24th month: Deliver ten (10) 4000-cm<sup>2</sup> (4-ft<sup>2</sup>) CIS-based commercial modules with AM 1.5 aperture-area efficiency of 10%.

- D4. End of the 24th month: Deliver ten (10) 4000-cm<sup>2</sup> (4-ft<sup>2</sup>) CIS-based commercial modules with AM 1.5 aperture-area efficiency of 10% for the NREL Module Testing Team.

#### Phase III

- D5. End of the 36th month: Deliver ten (10) 4000-cm<sup>2</sup> (4-ft<sup>2</sup>) CIS-based commercial modules with AM 1.5 aperture-area efficiency of 12%.

- D6. End of the 36th month: Deliver ten (10) 4000-cm<sup>2</sup> (4-ft<sup>2</sup>) CIS-based commercial modules with AM 1.5 aperture-area efficiency of 12% for the NREL Module Testing Team.

# **Technical Review**

# **Large Area Circuit Fabrication**

## **Circuit Plate & Module Statistics**

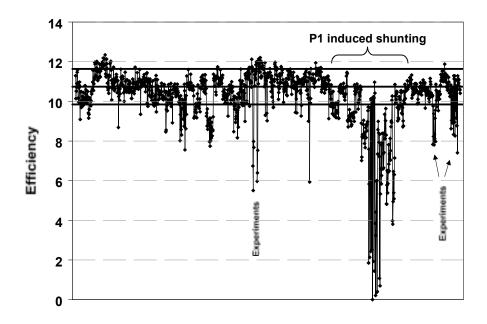

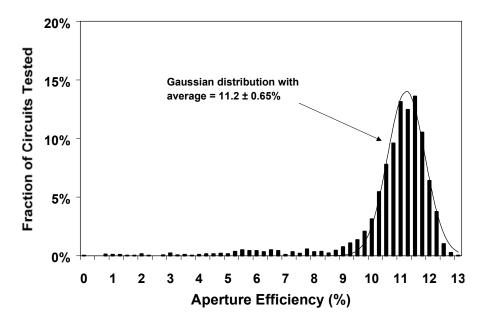

Circuit plate statistics representative of the beginning of this subcontract were compiled using data from a few months before and the early portion of this subcontract (Figure 6, Figure 7). During that time frame (January through November 1998), about 1300 ~30x120 cm circuit plates were produced including 18% that were dedicated to experiments [3, 14].

Figure 6. CIS Circuits Produced January through November 1998 (abscissa – module identifier).

Figure 7. CIS Circuit Efficiency Distribution - January through November 1998.

This process data demonstrates generally good control for extended periods with an average efficiency of 10.8% based on a Gaussian fit to the main portion of the distribution. Periodic shifts in the short-term average efficiency between about 10.25 and 11.25 resulted from shifts in  $V_{oc}$  and FF that were related to batch-to-batch variability in precursor or base electrode preparation. Similarly, periodic shunting along the laser scribed pattern lines in the Mo base electrode resulted from batch-to-batch variability in base electrode preparation.

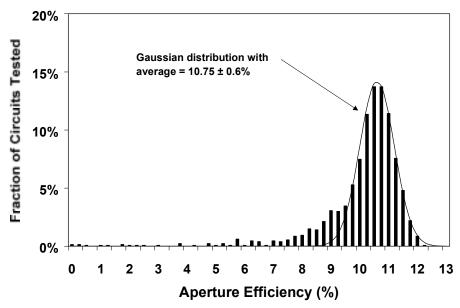

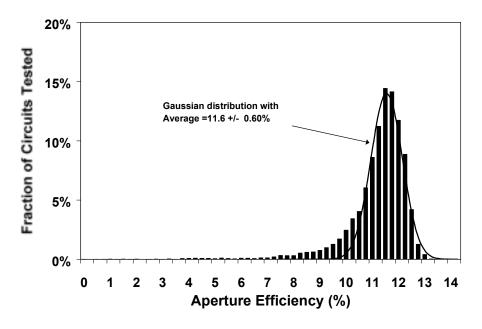

Similar data representative of the first phase of this subcontract is presented in Figure 8 and Figure 9. This timeframe corresponds with the SSI fiscal year (October 1998 through September 1999) and there is some overlap with the data presented in the previous charts. An average efficiency of 11.2% is demonstrated for 3,030 circuit plates.

Figure 8. CIS Circuits Produced October 1998 through September 1999 (abscissa – module identifier).

Figure 9. CIS Circuit Efficiency Distribution - October 1998 through September 1999.

This process data also exhibits generally good control for extended periods. The average efficiency based on a Gaussian fit to the main portion of the distribution increased from 10.8% to 11.2% in part due to better overall process consistency and in part due to changes in the reaction process. Small periodic shifts in the short-term average efficiency continued due to shifts in  $V_{oc}$  and FF resulting from batch-to-batch variability in precursor or base electrode preparation. Process development eliminated or greatly reduced periodic shunting along the laser scribed pattern lines. With the exception of identified special causes for irregular performance such as bad raw materials, 87% of the circuit plates were above 10% efficiency. Also during this timeframe, NREL confirmed a world-record 12.1 percent conversion efficiency for a large area  $(3651 \text{ cm}^2)$  CIS module.

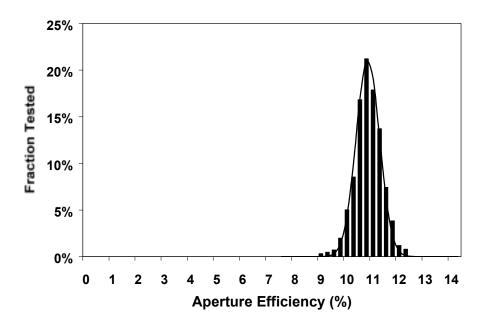

Progress during the second subcontract period (September 1999 through August 2000) included production volume increases of over 300% while also improving efficiency. Circuit plate data representative of the second subcontract period is presented in Figure 10. Efficiency improvements are again demonstrated with a peak in the Gaussian fit at 11.6%. Generally good process control is again demonstrated. The production distribution of modules (Figure 11) is sharply peaked at nearly 11% efficiency with a full width of only  $\pm$  0.5%.

Figure 10. CIS Circuit Efficiency Distribution - September 1999 through August 2000.

Figure 11. Module production distribution - September 1999 through August 2000.

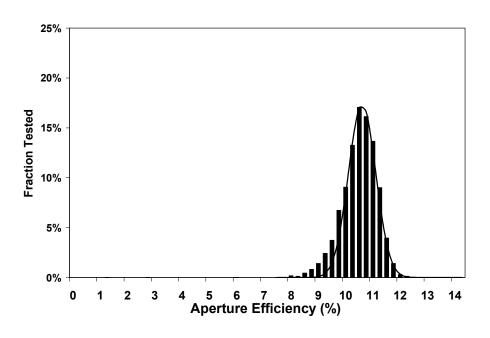

The distribution of production modules representative of the end of this subcontract (January through September 2001) is presented in Figure 12. The distribution includes data for 7583 laminates for a cumulative power of 292 kWp. The distribution is sharply peaked at nearly 11%. The peak of a Gaussian fit to the main portion of the distribution is at 10.6% with a standard deviation of 0.50%; the full width of the distribution is only 9% of the average.

Figure 12. Module production distribution - January through September 2001.

As summarized in the following table (Table 1), circuit plate production capacity has increased by more than an order of magnitude since the beginning of this subcontract while also improving circuit and module efficiencies. Initially lower performance when using new absorber formation reactors and new precursor sputtering equipment is responsible for the slightly lower efficiency and slightly broader distribution during the third phase relative to the second phase of this subcontract. Process development for new equipment and increased production capacity is discussed in later sections.

Table 1. Circuit production capacity and efficiency progress.

| Year  | Module Production (kW) | Average Aperture Efficiency |                     |

|-------|------------------------|-----------------------------|---------------------|

|       | , ,                    | Unlaminated<br>Circuit      | Laminated<br>Module |

| 97-98 | 15                     | 10.8%                       | 10.3%               |

| 98-99 | 68                     | 11.2%                       | 10.7%               |

| 99-00 | 294                    | 11.6%                       | 10.9%               |

| 00-01 | 486                    | 10.9%                       | 10.6%               |

|       |                        |                             |                     |

|       |                        |                             |                     |

Mechanical and electrical yield progress for baseline processing is as important as progress in circuit plate or laminate efficiency. Mechanical yield is defined as the fraction of all glass substrates originally introduced into the baseline circuit production sequence which then successfully pass all intermediate inspection criteria and are IV-tested. With this definition, mechanical yield quantifies the rejection of substrates for failures such as glass breakage, film scratches, or out-of-specification process runs. Overall line yield is the combination of mechanical and electrical yield and, since electrical yield is very high, the overall line yield is primarily limited by mechanical yield. During a timeframe representative of the first phase of this subcontract (May through September 1999), overall line yield analyzed on a monthly basis ranged from 32% to 61%. During a timeframe representative of the last phase of this subcontract (January through November 2001), overall line yield ranged from 56% to 89%. This dramatic improvement through the subcontract, although non-monotonic, was the result of addressing disparate causes of primarily mechanical losses.

Electrical yield is more subjective since it depends upon the choice of a lower specification limit. For example, at 10% minimum circuit efficiency, the yield of non-experimental circuits for the January through September 2001 timeframe (Figure 12) is 84%; at 9% minimum, the yield was over 98%. Electrical yield has been generally high throughout the subcontract with the exception of identified special causes that lowered yield for typically less than one month. Most

production modules have efficiencies above 10% and the overall electrical yield of the CIS production line at the end of this subcontract is nearly 98%!

Yield data for two timeframes, either of which could be considered representative of the end of this subcontract, is presented in the following table (Table 1). Electrical yield is high for both timeframes while the mechanical yield varies. Notably, the relative importance of mechanical loss mechanisms varies for the two timeframes. For example, operator error appears as one of the loss mechanisms exceeding 1% for the first timeframe and not for the second. Similarly, the equipment failure category typically includes failures of different equipment during different timeframes. Pealing is a loss mechanism that appears in both timeframes. Multiple process parameters that impact pealing were identified during this subcontract and process research and development mitigated but did not eliminated peeling losses. These are examples of the disparate special cause loss mechanisms that were addressed throughout this subcontract. Efficiency and yield advancements made during this subcontract are the result of production research and development through multiple cycles of learning.

Table 2. Yield data for two timeframes representative of the end of this subcontract.

|                  | June 2000 through<br>mid August 2001 |      | September 2001 through<br>January 2002 |      |

|------------------|--------------------------------------|------|----------------------------------------|------|

| Line Yield       | 64%                                  |      | 83%                                    |      |

| Electrical Yield | 92%                                  |      | 99%                                    |      |

| Mechanical Yield | 72%                                  |      | 84%                                    |      |

| Mecanical Losses |                                      |      |                                        |      |

|                  | <b>Equipment failure</b>             | 5.3% | Broken                                 | 3.7% |

|                  | Broken                               | 4.9% | Equipment failure                      | 2.9% |

|                  | Film peeling                         | 4.1% | Bad snap                               | 1.9% |

|                  | Scratch                              | 3.1% | Film peeling                           | 1.7% |

|                  | Operator error                       | 1.6% | Scratch                                | 1.4% |

|                  | Bad snap                             | 1.2% |                                        |      |

|                  | Lamination bubble                    | 1.1% |                                        |      |

|                  | All others                           | 4.4% | All others                             | 2.6% |

## **Process Development Examples**

This section and the following section titled "Module Packaging and Product Durability" will present examples of subcontract work with emphasis on major subcontract activities and collaboration with NREL. Examples are included for all major process steps. SSI's participation in the National CIS R&D Team is discussed in a later section. Team activities emphasized research topics common to multiple CIS R&D groups whereas the collaborations discussed in this section are generally more specific to SSI activities. Both types of collaborations with NREL have greatly contributed to SSI's progress. The following examples present an overview of subcontract technical accomplishments that were achieved while addressing substrate size and capacity scale-up, pursuing efficiency and yield advancements, and applying process research and development to identify special causes for process variation.

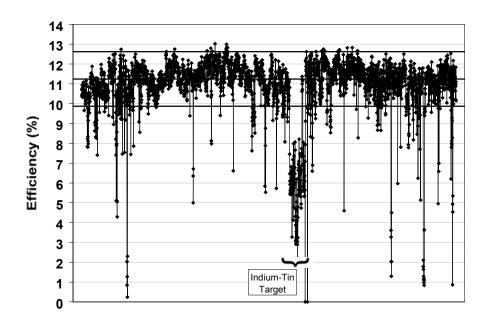

A major loss in production was caused by a serious quality lapse by the H<sub>2</sub>Se supplier. Instead of H<sub>2</sub>Se, the supplier delivered a cylinder, and subsequently yet another cylinder, of a gas with a much higher vapor pressure. This triggered overpressure relief valves, contaminated gas lines, interrupted production, and resulted in a general interruption of ongoing development activities. Another major loss of circuit plates occurred due to a similar problem with supplied materials. An indium-tin target was supplied instead of an indium target. Poor circuit performance resulted from this inadvertent test of changes in the relative concentrations of precursors and the addition of tin. These events introduced materials with extreme differences from specified materials and illustrated the vigilance required in obtaining the proper materials to achieve high yield.

In addition to being a process issue, the overpressure of gas lines was a potential safety issue. As part of SSI's efforts to promote safe operations throughout the photovoltaics community, SSI communicated results and insights regarding this incident to the photovoltaics community through the leaders of the TFPPP ES&H Team, Paul Moskowitz and Vasilis Fthenakis.

Process development for new absorber formation reactors was a major subcontract activity. In additional to first order requirements such as reasonable temperature uniformity within the absorber formation reactors, the importance of reactor design to the CIS formation process was demonstrated when first scaling from a baseline process in small area reactors to a large area reactor. SSI demonstrated that differences between baseline and the first large area absorber formation reactor design were responsible for differences in absorber layer properties and cell performance. These differences were isolated to differences in the materials of construction and the physical design of the large reactor. As a result of these studies and advances in understanding the influence of reactor design on performance, SSI designed and built a new large area reactor (the prototype large area reactor) based on a more direct scale-up of the baseline reactor. Success with this development effort was demonstrated by comparable performance for baseline and large area circuit plates.

During this subcontract, new production reactors were procured, process development for these reactors was begun and the reactors were ultimately qualified for production. Circuit plate production was increased even though more R&D resources than anticipated were expended on process development for new reactors. Implementation of the new reactors was delayed by late delivery from the equipment vendor. These reactors exhibited poorer reliability than the prototype large area reactor. A longer than anticipated process development cycle was required to qualify the reactors for production. Efforts throughout particularly the second and third

subcontract phases addressed warping and poor CIS to Mo adhesion for some plate locations within the reactors while simultaneously developing processes for increased circuit plate load.

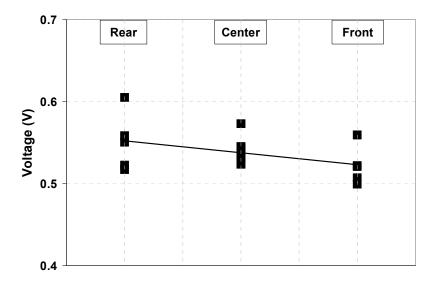

The following is an example of reactor process development efforts in collaboration with NREL to characterize the potential dependence of device performance on reactor position. Small devices fabricated by NREL on completed SSI devices (processing through ZnO at SSI) were used to characterize the potential dependence of device performance on reactor position for one of SSI's newer large area reactors. Performance versus temperature and position were analyzed using typical IV measurements (Eff, Voc, Jsc, FF).

Figure 13. Dependence of Voc on reactor position.

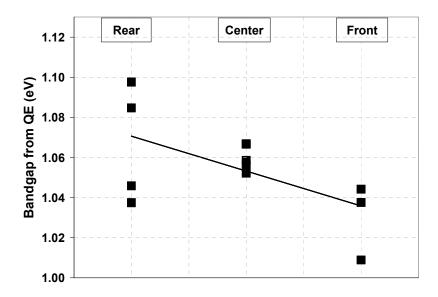

In addition, NREL-supplied quantum efficiency data was used to generate a measure of the potential dependence of bandgap on reactor position. The intercept on the energy axis of the square of quantum efficiency versus photon energy is taken as a measure of optical bandgap. This bandgap data is actually a qualitative measure of device structure since the measured bandgap is a convolution of the affects of absorption and collection through the varying bandgap structure of these absorbers. As with Voc, these bandgap measurements indicate a difference in the absorber structure dependent on position within the reactor; in this case, a statistically significant increase in bandgap from front to rear within the reactor is observed.

Figure 14. Dependence of bandgap on reactor position.

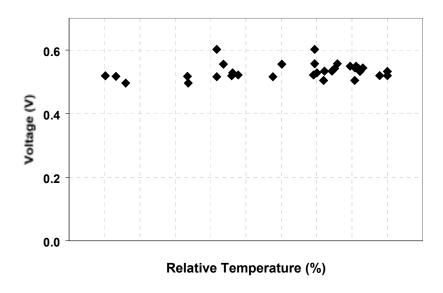

Temperature variations within the reactor are known from measurements using multiple thermocouples to profile temperatures throughout the reaction process. Although both Voc and bandgap are dependent on position within the reactor, there is no correlation between these parameters and the local temperature within the reactor. As when scaling from a baseline process in a small area reactor to the prototype large area reactor, this data implies that the local environment within the reactor, beyond simply the local thermal history, has an impact on the device structure and performance.

Figure 15. Lack of correlation between Voc and local temperature within the reactor.

Process development related to Mo deposition and the absorber formation process is another example of collaborations between NREL and SSI. SIMS and AES analysis support from NREL [15] was obtained for samples with a factor of two difference in the Mo thickness processed in both a large area reactor and a small area reactor. Minimal differences were seen in the elemental profiles of the major constituents (Cu, Ga, In, S, Se) for the two Mo thicknesses. With the exception of features that are assumed to be anomalous, the samples also exhibit minimal differences in the elemental profiles of the minor constituents. If observed differences by a factor of two to three in sodium and potassium are significant, the differences correlate with the reactors rather than the Mo thickness. The SIMS data set indicates anomalously high O<sub>2</sub> in one sample; however, the Auger data indicates that this high value is still below 1 to 2 atomic percent. The SIMS data also indicates a high Ca concentration in one sample. However, this signal is probably the result of contamination after formation of the absorber since the Ca profiles for all other samples but this sample exhibit structure in the Ca profile that parallels structure for other elements in the graded absorber. Results of this collaboration resulted in support for the decision to decrease Mo thickness and hence increase the capacity of Mo deposition equipment.

Subcontract work first with equipment existing at the start of this subcontract and then with new equipment led to predictable Mo deposition and P1 scribing processes for high throughput processing of large substrates. Process development with existing equipment demonstrated the impact of Mo deposition conditions on laser patterning and the dependence of scribe quality on laser patterning parameters. Through additional cycles of learning, process development for new Mo deposition equipment first demonstrated a process that permitted quality P1 scribes but with limitations on the number of plates that could be consistently processed. Additional process development led to another process modification that mitigated the limitation on the number of plates that could be consistently processed.

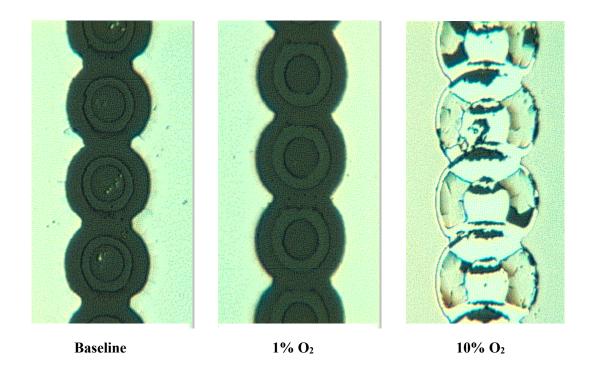

Prior to this subcontract work, shunting along laser P1 scribes sporadically caused poor performance. Studies of the interdependence of Mo properties and laser processing using existing equipment were conducted to address this issue. Studies to determine if laser scribing of Mo is affected by a background of  $O_2$  during Mo deposition is an example of this process development. Mo was sputtered with no  $O_2$  (baseline) and with  $O_2$  flowing at 1% and 10% of the Argon flow. Figure 16 illustrates that the visual appearance of scribes is not dramatically affected by 1%  $O_2$  but is distinctly affected by 10%  $O_2$  - the Mo deposited with 10%  $O_2$  is not completely removed. A similar trend was observed for mini-module performance. Performance differences between baseline and a 1% partial pressure of  $O_2$  were not statistically significant for the relatively small number of devices processed. The modules made with Mo deposited with a 10%  $O_2$  background could not be tested since the modules did not have complete P1 scribes.

Figure 16. The dependence of Mo scribe appearance on background O<sub>2</sub> during Mo deposition.

Studies of the impact of laser scribing parameters on scribe quality were also conducted. The following figure (Figure 17) represents the major features in Mo that has been affected by an individual laser pulse. A P1 scribe is generated by repeating this interaction forming multiple craters with an offset between adjacent craters. Mo is removed to a radius of R1. The Mo has been affected without removal in the region between R1 and R2 - referred to as the "affected Mo region."

Figure 17. Diagrammatic representation of the effect of an individual laser pulse.

Laser processing studies indicated that the dimensions of the region where Mo is removed are predictably modeled by laser parameters. Correlation between Mo deposition process

parameters and the extent of the affected Mo region were also demonstrated. The following summarizes the results of these studies and observations:

- The baseline process is not critically sensitive to laser focus the process depth of field is large relative to normally encountered variations in substrate surface position.

- Removal of Mo by a laser pulse is hindered by the presence of the affected Mo region from previous pulses; the presence of the affected Mo region can interfere with continuously connecting well-formed craters to achieve electrical isolation.

- Shunting can be caused by an extensive affected Mo region.

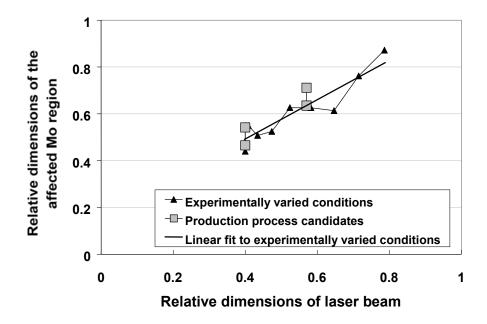

- The extent of the affected Mo region is dependent on Mo properties and laser parameters such as the relative dimensions of the laser beam. This is illustrated in the following chart (Figure 18), which demonstrates monotonically increasing relative dimensions of the affected Mo region as a function of the relative dimensions of the laser beam.

- Variations in quality of the laser-produced pattern are related to variations of the properties of Mo across 1x4 ft. substrates and batch to batch variations in Mo properties.

These Mo deposition and laser parameter studies resulted in the definition of predictable Mo deposition and P1 process for existing equipment.

Figure 18. Relative dimensions of the affected Mo region versus normalized laser beam dimensions.

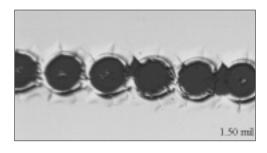

Initially, Mo deposited in a new high capacity sputtering system exhibited poor quality P1 scribes; craters had a more extensive affected Mo region. The following figure (Figure 19) illustrates scribes for Mo deposition conditions leading to poor and high quality P1 scribes. The

image on the left illustrates a poor quality scribe with an extensive affected Mo region. Based on process development using the older equipment, Mo deposition process modifications were made for the new sputtering system and consistently produced quality scribes were demonstrated. This process was adopted by production; however, at the expense of process complexity and process drift that limited throughput. Additional process options were explored and another unique sputtering process was developed. This led to generally well controlled and uniform patterning even at higher throughput.

Figure 19. Laser scribes for Mo deposition conditions leading to poor and high quality P1 scribes.

The laser processing discussed for first existing equipment and then new equipment illustrates the importance of multiple cycles of learning in production R&D. R&D to quantify the dependence of scribe quality on laser parameters and Mo deposition conditions was necessary to evaluate sporadic shunting along laser P1 scribes. The know-how derived from these studies in existing equipment was applied to process development for new high throughput production equipment when defining the first process for this equipment. Continuing experience with this process while scaling up production capacity illuminated process complexity and process drift issues that limited throughput. Additional process options based on previous experience were explored and another unique sputtering process was developed. These multiple cycles of learning led to a production qualified high throughput Mo deposition process for the new sputtering equipment and improved circuit electrical yield from about 90% to typically above 95%!

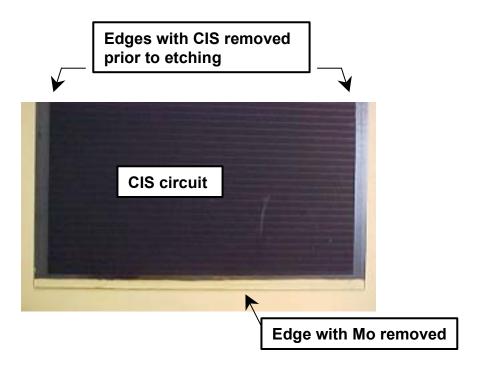

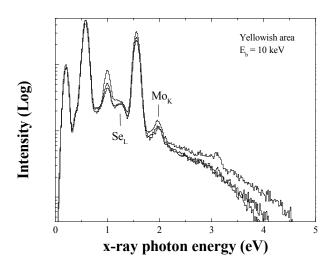

As an example of subcontract activities that did not lead to improvements in the baseline process, an etching technology used in the printed circuit board industry was tested as an alternative to laser scribing. The goals of this study were to demonstrate the process, compare shunting along P1 for laser ("L-P1") and etched ("E-P1") patterning, and demonstrate simultaneous processing of P1 and a wide Mo free border. The Mo free boarder is important for alternative module encapsulation configurations. The E-P1 process was tested in the full module fabrication process and physical features unique to the E-P1 process were analyzed with the help of NREL resources. Smaller than typical circuit plates (~30x30 cm) were used to accommodate available equipment.

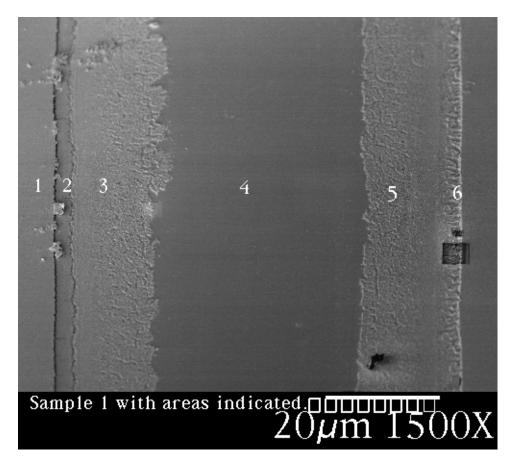

The visual appearance of E-P1 scribes motivated analysis of scribe features. A very thin transparent and insulating layer remains within some etched P1 scribes. Also, a narrow strip is present at the edge of all lines that appears to be similar to the thin layer. NREL supplied SEM

micrographs of E-P1 scribe features (Figure 20) and Auger and XPS analysis [16]. Features are numbered as follows in the SEM:

1 - Mo

2, 3, 5, 6 - thin transparent layer

4 - center of the E-P1 scribe

Figure 20. NREL supplied SEM of an etched P1 isolation via.

Auger analysis was complicated by sample charging; however, charging was less of a problem for area 2 than areas 3 through 5 since area 2 is close to the Mo. The following elements were identified for the areas labeled 1 and 2 on the numbered SEM.

Area 1; On the Mo Mo, C, O

Area 2; On the transparent insulator Mo, C, O, Ca, N, Fe

NREL also used XPS analysis however the dimensions of the probe beam are larger than the scribe width. Table 3 summarizes the results:

Table 3. XPS analysis of an etched Mo isolation scribe (percent concentration).

| Analysis Area               | С  | 0  | Мо | Na | Ca    | Si | S |

|-----------------------------|----|----|----|----|-------|----|---|

| Мо                          | 57 | 25 | 16 | 1  | 1     | 0  | 0 |

| Scribe including some<br>Mo | 60 | 23 | 12 | 1  | trace | 2  | 1 |

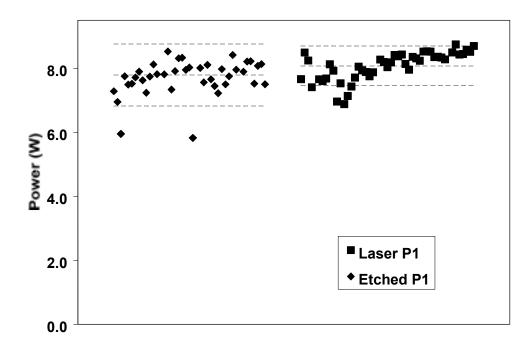

Module performance results are summarized in the following module power chart (Figure 21). The distribution of power for circuit plates with L-P1 is ~4 points better than the distribution for E-P1 and the difference is statistically significant. Differences in FF explain the majority of this difference. No definite but several possible causes for the low performance, including the analyzed narrow strip at the edge of all lines, were determined by observing circuit plates. It is assumed that elimination of these relatively small differences would be possible with in-house process development. The potential advantage of an E-P1 process for reducing sporadic shunting along P1 was not demonstrated since poor adhesion along P1 was not observed for either process during the time frame of this experiment. This alternative to isolation scribes produced with a laser was not adopted due to simultaneous improvements in the laser P1 process and commercialization issues for the etch process.

Figure 21. Module performance for laser and etched Mo patterning (abscissa – module identifier).

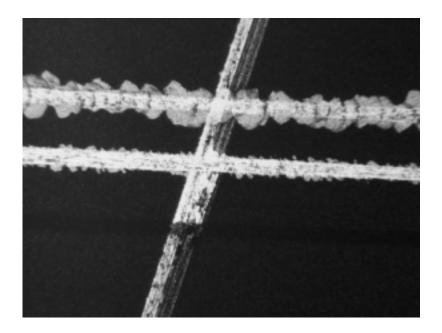

As another example of SSI/NREL collaborations, analysis at NREL [17] was particularly helpful in SSI's continuing efforts to identify the source of scratches. Scratches degrade performance and it is relatively easy to inspect just degraded modules and at times find scratches. However, it is difficult to inspect all large area modules during each stage of processing to determine when the scratches occur. Figure 22 is an optical micrographs illustrating a scratch across the interconnect patterns (patterns 1, 2 & 3). Acetic acid was used to remove the ZnO electrode. Similar CdS depositions are expected in the scratch and in pattern 2 if the scratch occurred before CdS deposition. EDS analysis did not find evidence of CdS in the scratch. This implies that, at least for this particular scratch, the scratch occurred after CdS deposition and before ZnO deposition.

Figure 22. Optical micrograph of a patterned and scratched area analyzed by NREL.

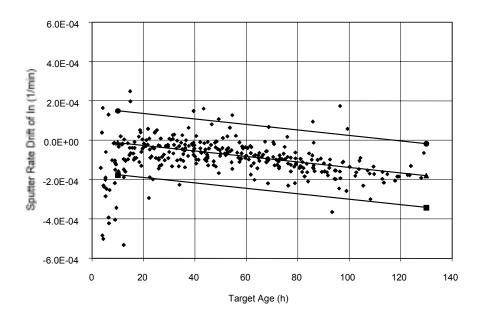

Significant improvements in control of the precursor deposition process were made during this subcontract period [18]. Precursor sputtering diagnostics characterize and lead to the control of the absorber thickness and the Cu/(In+Ga) ratio (CIG ratio) which are critical parameters in production of high efficiency CIS devices. Deposition of the metallic elements of CIS on production substrates occurs sequentially from two targets in an in-line sputtering system, first from a copper-gallium alloy target (17 at% Ga) and then from a pure indium target. The deposition rate of each target is measured using a modified quartz crystal technique; a quartz crystal is run through the sputtering system twice, the first pass for deposition of the copper-gallium film only, and the second for the indium film only. The resonance frequency of the quartz crystals is measured outside the vacuum system before and after each deposition pass and the thickness of copper-gallium and indium layers are calculated based on frequency differences before and after the depositions.

A set of 10 crystals is distributed across a substrate to characterize the uniformity of deposition across the substrate width. This is especially important since a shift in deposition uniformity for

either deposition can lead to regions of unacceptable CIG ratio even when the average composition appears acceptable. This measurement procedure is executed at the beginning of each production run to set the sputter rates within specifications. The measurement procedure is then repeated after a run of substrates for production. These pre- and post-run deposition rate data are the basis for production process control. A model including the effects of changes in sputter rate with target age predicts how sputter rates and thus CIG ratio drifts during a run of substrates. This model is applied to define the maximum duration for a run of substrates and determine when it is appropriate to change targets [18]. Subsequent R&D indicated that the process control parameters derived in this way are unique to a particular sputtering system.

Figure 23. Indium sputter rate drift.

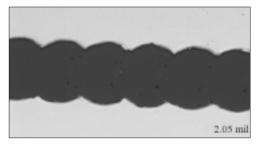

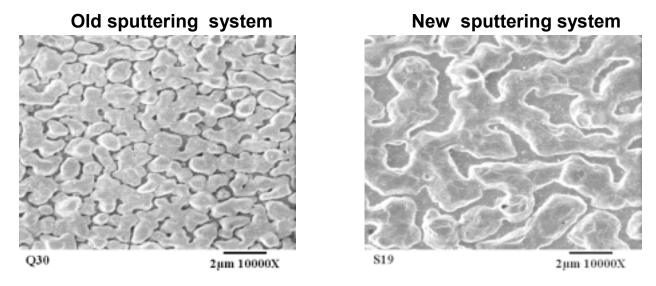

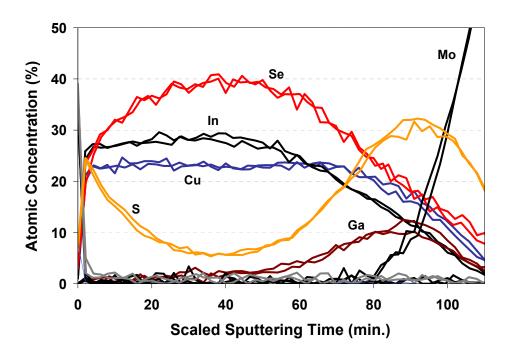

Process development for new high throughput base electrode and precursor sputtering equipment (Figure 24) was required to achieve circuit plate performance similar to the performance for precursors deposited using older and lower throughput equipment. Initial results for precursors from the new sputtering system indicated lower efficiencies primarily due to lower FF. NREL assisted with this process development by supplying SEM and Auger depth profile analysis of precursors from the two sputtering systems. As illustrated in Figure 25, precursor surface morphology differences were observed. Auger analysis (Figure 26) indicates that the achieved elemental depth profiles are independent of the sputtering system used to deposit the precursors. This development work led to a process in the new high throughput base electrode sputtering equipment that achieves FF's similar to (within 4%) results from the older equipment.

Figure 24. New high throughput base electrode and precursor sputtering equipment.

Figure 25. Precursor morphology dependence on sputtering conditions.

Figure 26. Nearly identical elemental profiles for two samples from two sputtering systems.

Additional precursor process development indicates that efficiency improvements are possible for thicker absorbers after improving adhesion. Increases in efficiency were demonstrated for thicker absorber layers as summarized in Table 4. Efficiency increases of 12% and 15% respectively are observed for absorber layer thickness increases of 125% and 150% of the baseline thickness. These gains based on circuit plate measurements are somewhat inflated relative to the results expected for laminates. Poorer adhesion correlated with both increased thickness and plate position within the reactor.

Table 4. Circuit performance versus absorber thickness.

|                  | Change Relative to Baseline |    |     |     |  |  |  |  |

|------------------|-----------------------------|----|-----|-----|--|--|--|--|

| Thickness        | Eff FF Jsc V                |    |     |     |  |  |  |  |

| 125% of baseline | 12%                         | 9% | 3%  | 0%  |  |  |  |  |

| 150% of baseline | 15%                         | 9% | 10% | -1% |  |  |  |  |

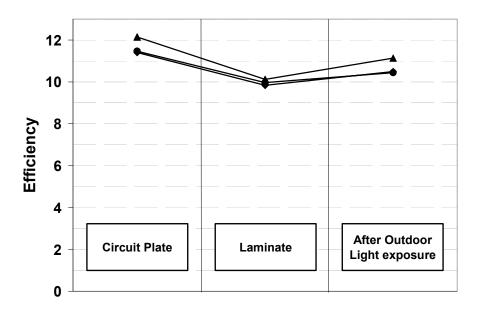

The following charts illustrate the dependence of module performance on doping concentration during ZnO CVD. Modules with otherwise common process steeps were fabricated with baseline dopant concentrations and dopant concentrations above and below baseline conditions. ICP analysis indicates achieved dopant concentrations relative to baseline conditions of 55%, 100%, and 116%. Performance measurements were made after fabrication, after lamination and after two days of outdoor exposure. Circuit plate measurements were made using a constant light source solar simulator after about 100 seconds of light exposure and biasing near the maximum power point. Laminate measurements were made using a flash lamp solar simulator after biasing near the maximum power point for about seven seconds. The results indicate an approximately five percent performance improvement for the lower doping concentration and these conditions were adopted as updated baseline conditions.

Figure 27. Circuit plate and laminate performance for ZnO doping relative to baseline conditions of 55% (▲), 100% (♦), and 116% (●).

In addition to these examples, process R&D for performance improvements and capacity scale up has included:

- Addressing major yield issues such as scratches, mechanical yield, operator errors, equipment malfunctions and improper setup

- Demonstrating and addressing loss of FF with lamination related to capacity scale up of the CdS deposition process.

- Background exploration of XRF analysis as a replacement for measurements using quartz crystals to monitor the Cu/(In+Ga) ratio for precursors

- Dependence of precursor quality on long term execution of the sputtering process

- Dependence of precursor quality on alternative target configurations, sputtering system hardware and sputtering target vendor selection

- Dependence of electrical performance on the ratio of Cu/(In+Ga)

- Demonstration and addressing performance losses related to the use of plastic boxes for transporting plates.

- Exploring the possibility of replacing CVD ZnO with sputtered ZnO.

- Qualification of a new continuous light-source tester for 1x4 ft. circuit plates and the elimination of an outdoor light exposure prior to circuit plate measurement.

- Process options for Glass/glass packaging of small modules for low-voltage (< 48V) applications.

- Exploration of process options for Mo removal from the edge of circuit plates as one of the process developments necessary to implement glass/glass packaging options

# Module Packaging and Product Durability

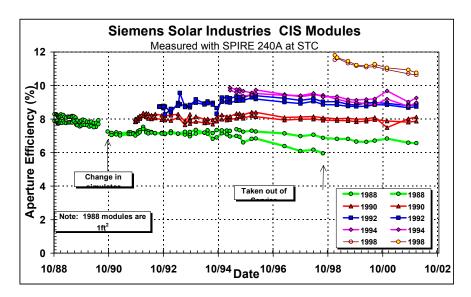

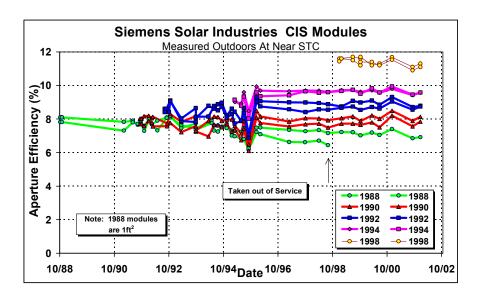

NREL supports SSI through long term testing of arrays and individual modules at the NREL Outdoor Test Facility. SSI has supplied modules of increasing size and efficiency for testing since 1988. The measurements in Figure 28 were made by bringing modules indoors, performing the measurements under standard test conditions using a pulsed solar simulator, and then returning the modules to their outdoor test location. Long-term outdoor stability has been demonstrated at NREL where ~30x30 cm and ~30x120 cm modules have undergone testing for over thirteen years.

Figure 28. NREL OTF long term outdoor stability measurements - pulsed solar simulator.

NREL measurements for long term stability testing also include outdoors measurements made near standard test conditions. SSI CIS modules exhibit transient effects that can confound the interpretation of data particularly for pulsed solar simulators [3]. Parallel data from NREL outdoors measurements near standard test conditions is presented in Figure 29. As is typical for CIS, continuous illumination measurements such as outdoor measurements indicate less variation in performance with time for all modules tested.

Figure 29. NREL OTF long term outdoor stability measurements - outdoors measurements.

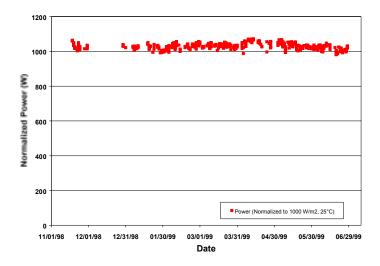

SSI has supplied modules to the NREL OTF for three 1kW arrays. In each case, a newer generation of modules has been used to replace older designs using the same test site. Data acquisition began on November 18, 1998 for the third 1kW array of modules. The system is comprised of 28 modules with an average efficiency of 11.4% at STC. The aperture area of each module is  $0.3651\text{m}^2$  and of the total array is  $10.2\text{ m}^2$ . The array is fixed at a  $40^\circ$  tilt aligned true south and is connected to a resistive load through 3 maximum power trackers.

Data from late February of 2000 indicates stability within 2% of the measurements made shortly after array deployment (Ben Kroposki, STR00SSI.001). Figure 30 summarizes NREL measured performance data for operation through June 30, 1999. The data is corrected for temperature and restricted to incident solar irradiance of between 950-1050 W/m². The array remained stable and has an average power normalized to standard test conditions of 1028 W. As for previous arrays, both module and the array data show good stability with no seasonal variation in performance. It can not be overemphasized that these studies demonstrate that thermally induced transients, which are observed after exposure to accelerated environmental testing conditions, are not observed in the field despite daily and seasonal changes in module temperature.

Figure 30. Temperature corrected power vs. time for the third 1kW array delivered to the NREL OTF in 1998.

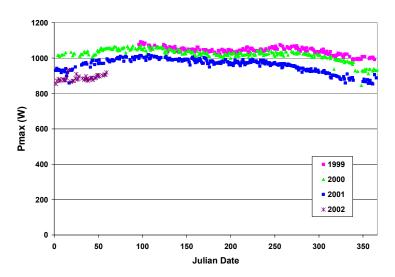

More recent array data from the OTF analyzed by SSI (Figure 31) indicates that the latest array may exhibit changes with time related to changes in module package design or process changes since deploying earlier arrays. NREL supplied pulsed simulator, continuous illumination simulator, and outdoor measurement data for six of the modules from the array. This data indicates that changes in performance are primarily changes in FF and, typical of CIS, observed changes are smaller for measurements made with continuous illumination or outdoors than for pulsed simulation. For this small sample of six modules, the change in FF is highly variable ranging from within the noise of the initial and recent measurements, 4%, to 18%. All modules do not degrade which may imply that changes are related to the interim package design for these modules. Alternatively, the changes for this array may be related to process changes made since installation of the first array, which was deployed for a similar time and did not exhibit these changes.

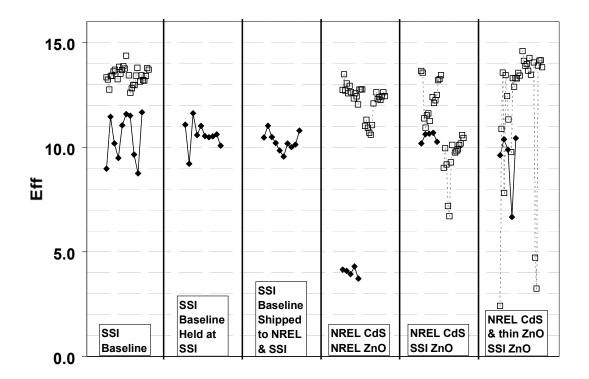

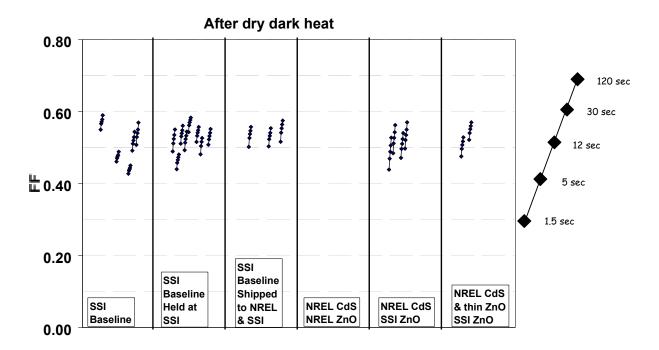

Figure 31. SSI analysis of OTF data for temperature corrected power vs. Julian date for the third 1kW array delivered to the NREL OTF in 1998.