# Optimization of Processing and Modeling Issues for Thin Film Solar Cell Devices

Final Report 24 August 1998—23 October 2001

R.W. Birkmire, J.E. Phillips, W.N. Shafarman, E. Eser, S.S. Hegedus, B.E. McCandless, R. Aparicio, and K. Dobson *University of Delaware Newark, Delaware*

1617 Cole Boulevard Golden, Colorado 80401-3393

NREL is a U.S. Department of Energy Laboratory Operated by Midwest Research Institute • Battelle • Bechtel

Contract No. DE-AC36-99-GO10337

# Optimization of Processing and Modeling Issues for Thin Film Solar Cell Devices

Final Report 24 August 1998—23 October 2001

R.W. Birkmire, J.E. Phillips, W.N. Shafarman, E. Eser, S.S. Hegedus, B.E. McCandless, R. Aparicio, and K. Dobson *University of Delaware Newark, Delaware*

NREL Technical Monitor: B. von Roedern

Prepared under Subcontract No. ZAK-8-17619-33

1617 Cole Boulevard Golden, Colorado 80401-3393

NREL is a U.S. Department of Energy Laboratory Operated by Midwest Research Institute • Battelle • Bechtel

Contract No. DE-AC36-99-GO10337

#### **NOTICE**

This report was prepared as an account of work sponsored by the National Renewable Energy Laboratory, a Division of the Midwest Research Institute, in support of its contract number DE-83CH10093 with the United States Department of Energy. Neither the National Renewable Energy Laboratory, the Midwest Research Institute, the United States Government, nor the United States Department of Energy, nor any of their employees, nor any of their contractors, subcontractors, or their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness or usefulness of any information, apparatus, product or process disclosed or represents that its use would not infringe on privately owned rights.

Available electronically at http://www.doe.gov/bridge

Available for a processing fee to U.S. Department of Energy and its contractors, in paper, from:

U.S. Department of Energy Office of Scientific and Technical Information P.O. Box 62 Oak Ridge, TN 37831-0062

phone: 865.576.8401 fax: 865.576.5728

email: reports@adonis.osti.gov

Available for sale to the public, in paper, from:

U.S. Department of Commerce National Technical Information Service 5285 Port Royal Road Springfield, VA 22161

phone: 800.553.6847 fax: 703.605.6900

email: orders@ntis.fedworld.gov

online ordering: <a href="http://www.ntis.gov/ordering.htm">http://www.ntis.gov/ordering.htm</a>

#### SUMMARY

The overall mission of the Institute of Energy Conversion is the development of thin film photovoltaic cells, modules, and related manufacturing technology and the education of students and professionals in photovoltaic technology. The objectives of this 20 month NREL subcontract are to advance the state of the art and the acceptance of thin film PV modules in the areas of improved technology for thin film deposition, device fabrication, and material and device characterization and modeling, relating to solar cells based on CuInSe<sub>2</sub> and its alloys, on a-Si and its alloys, and on CdTe.

#### CulnSe<sub>2</sub>-BASED SOLAR CELLS

#### Effect of Deposition Temperature on Cu(InGa)Se<sub>2</sub> Films and Devices

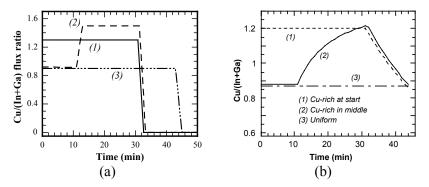

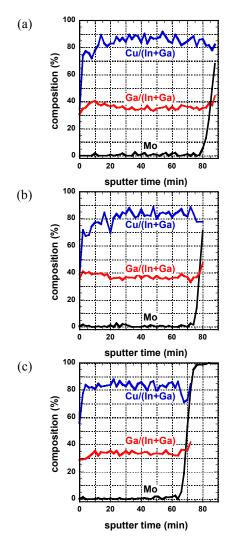

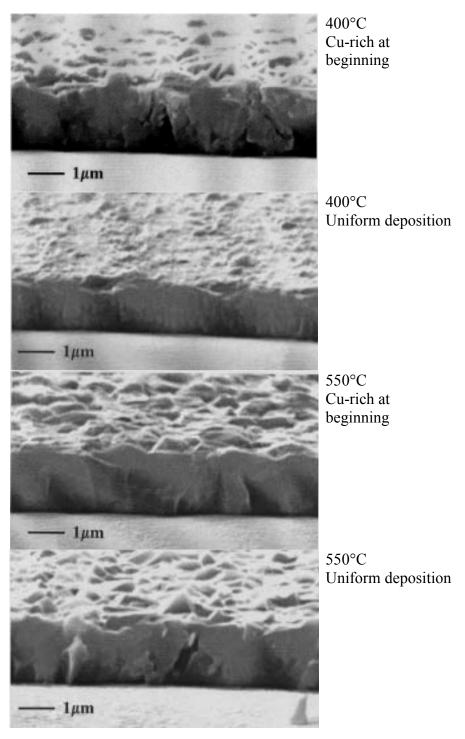

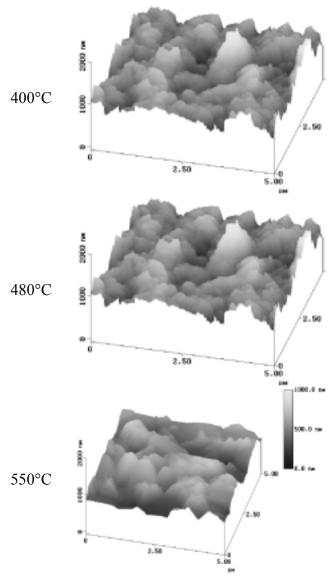

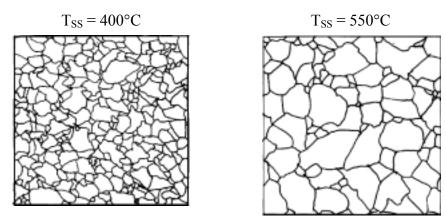

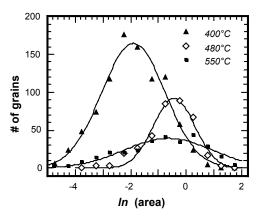

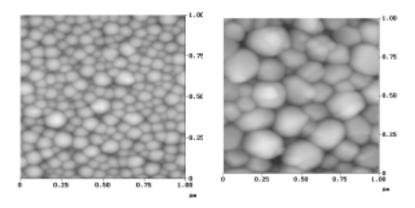

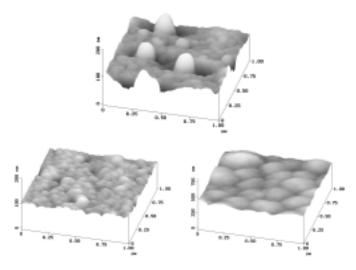

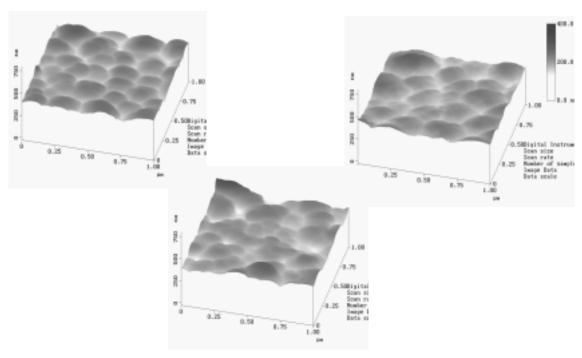

Lowering the  $Cu(InGa)Se_2$  substrate temperature from 550 - 600°C, used for the highest efficiency devices can reduce processing costs associated with glass handling and thermal stress on the deposition system, and potentially enable polyimide substrates to be used. The effects of substrate temperature and evaporation sequence, with regard to Cu-rich film growth on  $Cu(InGa)Se_2$ , films and devices and to quantitatively determine the effect of grain size.  $Cu(InGa)Se_2$  films were deposited by elemental evaporation of Cu, In, Ga, and Se using three flux versus time profiles to give depositions with: (1) Cu-rich flux, Cu/(In+Ga) > 1, at the start of the run, (2) Cu-rich flux in the middle of the run, and (3) uniform fluxes so that the films composition is never Cu-rich. The final composition of all devices was the same at the completion of the deposition. These depositions were each done with substrate temperatures  $(T_{SS}) = 400$ , 480, and 550°C. The grain size distribution and surface morphology of each  $Cu(InGa)Se_2$  film was determined using atomic force microscopy and compared to the device behavior.

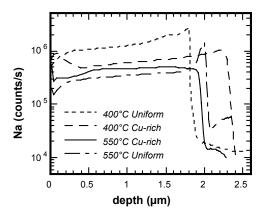

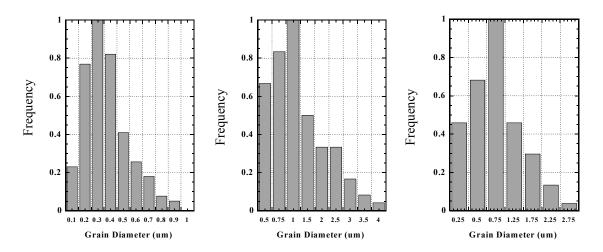

The highest efficiency devices in this study were 16.5% at  $550^{\circ}$ C and 14.1% at  $400^{\circ}$ C. Comparing different flux profiles, it was shown that at  $400^{\circ}$ C Cu-rich growth is necessary to achieve good performance. However, at higher  $T_{SS}$  the device performance is insensitive to the growth sequence allowing greater process flexibility. With the Cu-rich growth, the mean lateral grain area decreases from 1.8 to  $0.3~\mu\text{m}^2$  as  $T_{SS}$  is reduced from 550 to  $400^{\circ}$ C, but only at the highest  $T_{SS}$  does the grain size depend on the growth process. In general, lower device efficiency with lower  $T_{SS}$  cannot be simply described by changes in grain size, surface area or the availability of Na. Instead, the lower voltage and increased recombination current with lower temperature deposition indicate a greater density of intra-grain trap states in the  $Cu(InGa)Se_2$  which can also lead to smaller minority carrier diffusion length and voltage dependent current collection.

#### In-line Evaporation of Cu(InGa)Se<sub>2</sub>

In-line evaporation is a potentially effective means to achieve the high rate uniform deposition necessary for commercial-scale manufacture of Cu(InGa)Se<sub>2</sub> modules. In this process, the substrate is linearly translated over thermal sources from which the elemental materials are evaporated. An in-line evaporation system for the deposition of Cu(InGa)Se<sub>2</sub> films has been put into operation at IEC. The system's performance in terms of uniform deposition over large areas

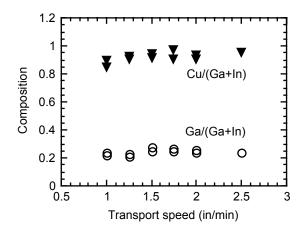

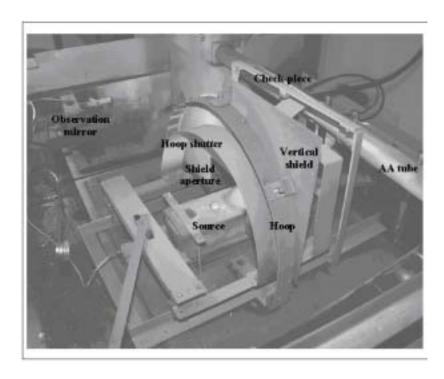

at relatively high rates and in terms of device performance and reproducibility has been successfully demonstrated. The compositional uniformity across the 6-inch wide deposition zone is within the uncertainty limits of EDS measurements. A set of depositions with translation speeds ranging from 1 to 2.5 inches/min produced films with thicknesses from 2.1 to 0.9  $\mu$ m thick. Devices from these runs had efficiencies from 13.2-14.5 %, for thickness > 1  $\mu$ m, demonstrating the run-to-run reproducibility of the system. The best cell produced with Cu(InGa)Se<sub>2</sub> from this in-line system had 14.9% efficiency. Improvements to the design and control of in-line evaporation process included improved source design, source characterization, and *in-situ* AA modeling and characterization. Combined, these achievements allow a high degree of controllability over the incident fluxes at the substrate over extended runs.

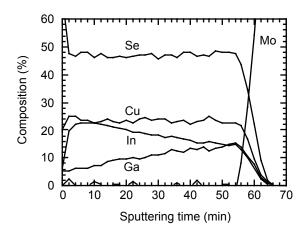

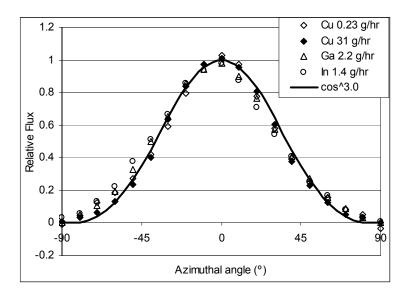

The spatial flux distributions from each of the Cu, In, and Ga evaporation sources, and over a wide range of evaporation rates for the Cu source, were measured. In all cases the flux could be describe by a  $\cos^n\theta$  approximation with n=3.0. A source effusion model predicting film thickness, composition, and compositional gradients was developed using the flux distributions and tested. In conjunction with Auger depth profiles, the model and film results show that Cu diffuses freely through the film, while Ga and In maintain graded profiles consistent with their sequence of deposition.

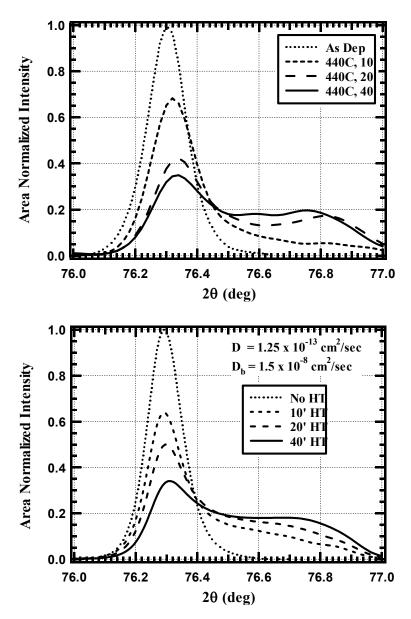

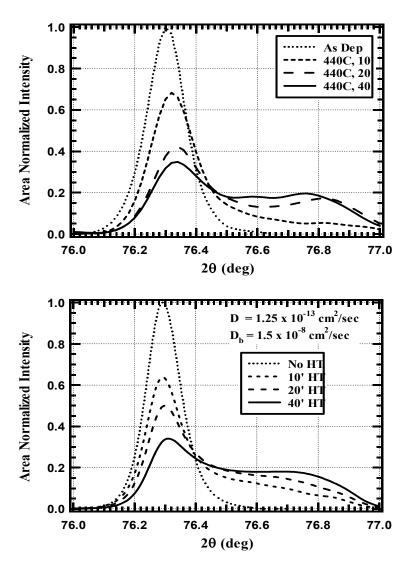

#### Formation and Analysis of Graded CuIn(SeS)2 and CuGa(SeS)2 Films

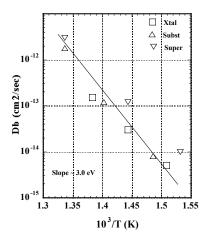

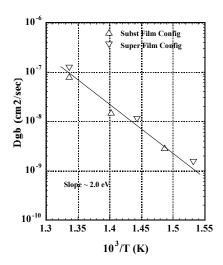

The incorporation of sulfur into CuInSe<sub>2</sub> thin films was quantitatively investigated to establish a scientific and engineering basis for the fabrication of homogeneous and compositionally graded CuIn(SeS)<sub>2</sub> thin films. By reacting stoichiometric or slightly Cu-rich CuInSe<sub>2</sub> films in a flowing H<sub>2</sub>S/Ar atmosphere, the films can be completely converted to CuInS<sub>2</sub> or converted to a graded CuIn(Se<sub>1-y</sub>S<sub>y</sub>)<sub>2</sub> film, depending on processing conditions. A phenomenological model of the reaction/diffusion process was developed wherein H<sub>2</sub>S reacts with CuInSe<sub>2</sub> at the surface to form CuInS<sub>2</sub>, releasing Se. The CuInS<sub>2</sub> and CuInSe<sub>2</sub> layers interdiffuse, resulting in a S/Se gradient in the structure. X-ray diffraction (112) line profiles of graded films are compositionally broadened due to continuously changing lattice parameters. The 3-dimensional sulfur distribution was calculated for measured grain size distribution using generated diffraction line profiles. These were fit to measured line profiles using bulk and grain boundary diffusion coefficients as fitting parameters, yielding diffusion coefficients and activation energies for bulk and grain boundary diffusion processes.

The effect of initial film composition and substrate in the sulfurization of  $CuInSe_2$  was further investigated.  $CuInSe_2$  films deposited on either soda-lime glass (SL) or Corning 7059 borosilicate glass (7059) substrates were reacted in flowing  $H_2S$  for times from 1 to 8 hours. Films with Cu-rich composition, Cu/In > 1, reacted for 1 hour, had nearly all the Se replaced by S. For Cu-poor films, the incorporation of S was significantly reduced. In addition, in Cu-poor films on SL glass,  $CuInS_2$  and  $NaInS_2$  were found at the film surface. These phases were not detected in films on 7059 substrates or in Cu-rich films. A phenomenological model has been proposed to explain the formation of segregated surface phases in Cu-poor films on SL substrates.

#### CuInSe<sub>2</sub> Team Participation and Collaborations

IEC was an active member of the following four sub-teams under the National CIS Team for the NREL Thin Film Partnership program:

Global Solar Energy. This team focused on helping GSE develop a low temperature process for the roll-to-roll deposition of Cu(InGa)Se<sub>2</sub>. IEC has provided direct support through materials characterization and device fabrication and characterization on both glass and flexible substrates. In addition, IEC and GSE have collaborated on several issues related to the in-line and roll-to-roll deposition of Cu(InGa)Se<sub>2</sub>. This included application of chemical surface deposited (CSD) CdS, as described in the CdTe section of this report. Cu(InGa)Se<sub>2</sub> devices, using absorber layers deposited at IEC and GSE, were fabricated with CSD CdS and shown to have comparable efficiency. The CSD process was shared with GSE.

<u>ISET</u>. IEC has assisting in the development of improved performance of ISET's CIS-based materials by investigating the use of sulfur incorporation to increase the voltages in devices and modules.

<u>Siemens Solar Industries</u>. This sub-team addressed reliability and transient effects in SSI's cells and modules. IEC provided device fabrication and characterization for other team members and supplying Cu(InGa)Se<sub>2</sub> films and devices for characterization.

<u>UNISUN</u>. IEC has provided detailed materials characterization, device fabrication and device characterization to support Unison's development of particle-based processes for deposition of Cu(InGa)Se<sub>2</sub>.

In addition to these activities in support of the national CIS Teams, IEC has provided direct support to several other groups within the Thin Film Partnership. Some specific activities have included:

<u>Florida Solar Energy Center</u>. IEC has done detailed J-V and QE measurements and analysis of FSEC's CuIn(SeS)<sub>2</sub> devices.

<u>University of Florida</u>. IEC has provided  $Cu(InGa)Se_2$  absorber layers, and fabricated and characterized solar cells using  $In_x(OH,S)_y$  buffer layers deposited by chemical bath deposition at UF [1].

<u>University of Illinois.</u> IEC developed a process to fabricate solar cells on Cu(InGa)Se<sub>2</sub> epilayers grown on GaAs substrates at University of Illinois. This process includes a Pt back contact and takes advantage of the conductivity of the GaAs. The best cell to date on the epilayers had efficiency > 7%.

<u>University of Oregon</u>. IEC is collaborating with the University of Oregon to quantitatively characterize the defects in working Cu(InGa)Se<sub>2</sub> solar cells using admittance spectroscopy. IEC has provided device samples encompassing a range of different Cu(InGa)Se<sub>2</sub> parameters including Ga content, deposition temperature and process and JV behaviors. Initial results showed that high efficiency devices have both band tails and a deep defect band [2]

<u>Washington State University.</u> IEC has continued to fabricate and characterize devices using alternate window layers being developed at WSU, focusing on MOCVD grown ZnSe and ZnO buffer layers [3].

#### Si-BASED SOLAR CELLS

Several investigations concerning a-Si solar cells and hot wire chemical vapor deposition (HWCVD) films were conducted during this contract. In the area of a-Si solar cells, the deposition of more conductive  $\mu$ c-Si p- and n-layers based on silicon carbide and silicon oxide was studied. The dependence of various commercial SnO<sub>2</sub> substrates to thermal and H<sub>2</sub> treatments was also investigated. In addition, two novel methods to characterize the contact resistance and junction properties of the transparent conductive oxide (TCO)/p contact in active p-i-n devices were developed. A key result from this analysis was that ZnO does not result in a blocking or high resistance contact as was commonly assumed. This work was done in collaboration with Dr. Gautam Ganguly at BP Solar. Finally, we completed a comprehensive study of optical enhancement and losses in a-Si p-i-n solar cells, determining the effect of TCO texture, back contact reflectivity and i-layer thickness on the optical enhancement factor. We conclude from this that parasitic absorption in the textured SnO<sub>2</sub> is a major loss, in addition to parasitic absorption at the back contact.

Regarding HWCVD Si films, two papers, summarizing the results of the deposition and characterization of HWCVD Si films and the modeling of the HWCVD process, were published in the *Journal of Industrial and Engineering Chemistry Research*. Key results from this work are that polycrystalline Si films can be deposited by HWCVD with pure silane and that there is a critical value of the atomic hydrogen to silane radical ratio at which the transition from amorphous to polycrystalline films occurs. In addition, several approaches were also investigated to enhance the grain size of HWCVD films. Preliminary results of an *in-situ*, low temperature metal induced crystallization method appears to produce films with micron size grains and no contamination by Al in the Si layer as determined by EDS.

#### Microcrystalline p-layers Based on Silicon Carbide and Silicon Oxide

The focus of the a-Si research was on deposition of more conductive  $\mu$ c-Si based p-layers and characterizing properties of TCO layers following plasma exposure. The Si:C:H and Si:O:H p-layers were deposited by RF CVD. The effect of H<sub>2</sub>, SiH<sub>4</sub>, CH<sub>4</sub> and CO<sub>2</sub> flow rates, boron dopant source gas, and RF power on microcrystallinity and conductivity was studied. This work is motivated by the need for a wide bandgap highly conductive p-layer material to simultaneously increase V<sub>oc</sub> and blue response of superstrate p-i-n solar cells.

The investigation of glow discharge deposited crystalline p-layers was conducted in two stages. First, we investigated the deposition and characterization of these types of films having a high level of CH<sub>4</sub> in the feed gas, which completed the investigation of carbon containing p-layers. The goal was to determine the feasibility of obtaining crystalline SiC phases in the films. Second, we investigated the deposition and characterization of films having CO<sub>2</sub> in the feed gas. The goal here was to obtain two-phase films of crystalline Si imbedded in a matrix of a—Si:O:H:C. The idea is that such films incorporated in p-i-n type devices could give high currents due to the transparency of the amorphous phase and high voltages due to the highly conductive

crystalline phase with a smaller junction surface. Also, the presence of CO<sub>2</sub> in the glow discharge plasma would tend to decrease the reducing effects of the plasma on the thin conductive oxide used as the front contact in superstrate devices.

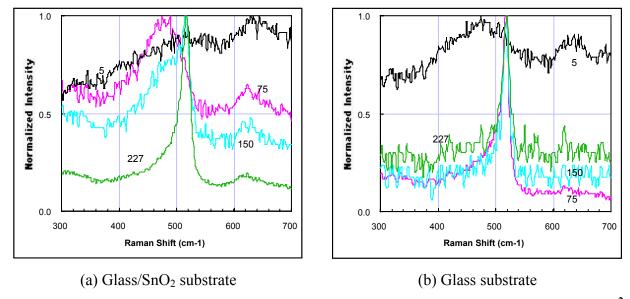

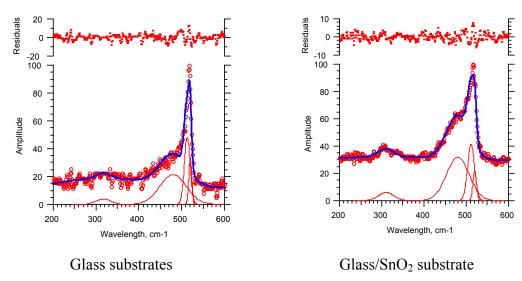

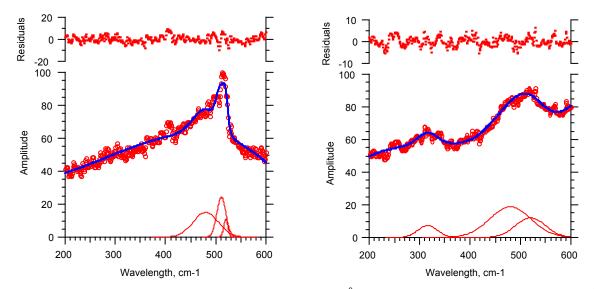

The p-layers were deposited on 7059 glass and on SnO<sub>2</sub> substrates, and their crystallinity was determined by Raman spectroscopy. In-plane conductivity and activation energy measurements were also performed on most of the films deposited on glass substrates.

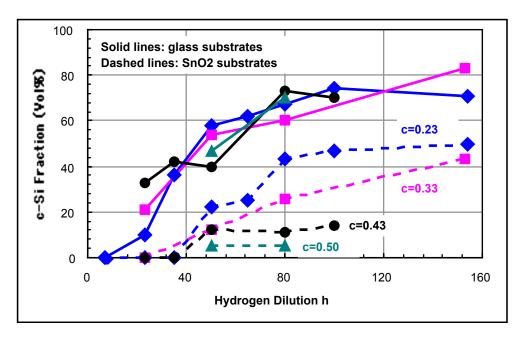

The main experimental variables were the hydrogen dilution and  $CH_4$  or  $CO_2$  content in the feed gases. The secondary parameters were discharge power density and doping gas  $(B_2H_6)$  level. Increasing hydrogen dilution reduces deposition rate even though silane partial pressure and gas residence time stay the same. This observation supports hydrogen etching of the film during growth. The observed increase in deposition rate with gas phase diborane concentration is related to the known ability of diborane in cracking silane molecules. Results also show that while the  $CO_2$  level in the discharge does not seem to have an effect on the c-Si content in the case of glass substrates, it does, however, control crystallinity of the films deposited on  $SnO_2$  substrates.

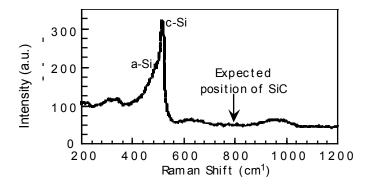

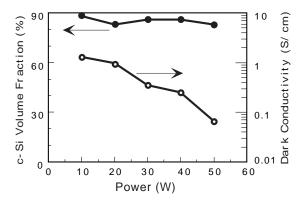

The only crystalline phase identified for films with CH<sub>4</sub> or CO<sub>2</sub> was silicon. Volume fraction of the crystalline phase was found to depend on hydrogen dilution but not on the discharge power. High silane partial pressures resulting in high deposition rates suppress the formation of the crystalline phase. High levels of crystallinity were obtained at very low power densities. Crystallinity in the films was found to decrease with increasing amounts of CO<sub>2</sub> in the discharge. The amount of crystalline phase in the films deposited on SnO<sub>2</sub> was consistently lower than in the films deposited on glass substrates. Raman spectra showed the existence of a two-phase mixture consisting of c-Si and amorphous silicon phases. Also, the film deposited on glass seems to have a higher amount of c-Si phase.

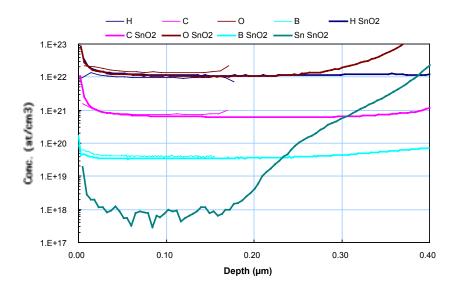

SIMS depth profiles indicate that the composition of the films are independent of the substrate, and the oxygen and carbon content in the films are, respectively,  $10^{22}$  and  $7x10^{20}$ . Since the films have a c-Si and an amorphous phase, the latter must contain almost all the hydrogen, carbon and oxygen observed in the SIMS analysis. Thus, it can be concluded that the amorphous phase is essentially hydrogenated silicon oxide containing small amounts of carbon and boron.

It is found that the fraction of c-Si increases with increasing hydrogen dilution and decreases with increasing diborane level. However, this observation is complicated by the dependence on the film deposition rates. This is because bonding rearrangement on the surface of the growing film that favors c-Si formation will be more extensive for low deposition rates. Consequently, dependence of crystallinity on hydrogen dilution is only clear in the regions where deposition rates do not change appreciably. The deposition rate argument can also explain the difference in crystallinity between like substrates deposited at different diborane levels.

However, the difference in crystallinity between glass and tin oxide substrates for a given diborane level might also be controlled, in addition to deposition rate, by the possible difference in the initial nucleation rate of crystallites on glass and tin oxide surfaces. The difference in deposition rates between glass and SnO<sub>2</sub> substrates is most probably due to the voltage difference between substrate and the plasma. In the case of a conductive substrate, such as SnO<sub>2</sub>, the

surface is grounded and the potential difference between substrate and plasma is the plasma potential. In the case of glass substrate, the potential difference is the floating potential which, in general, is substantially smaller than the plasma potential.

Increasing hydrogen dilution reduces the deposition rate even though silane partial pressure and gas residence time stay the same. This observation supports hydrogen etching of the film during growth. Finally, the observed increase in deposition rate with gas phase diborane concentration is related to the known ability of diborane in cracking silane molecules.

Interpretation of the measured conductivities and activation energies is problematic because of the two-phase nature of these films. However, it can be pointed out that measured activation energies of 0.07 eV are, within experimental errors, that of boron in silicon and, as such, confirm that in this respect silicon crystallites in the films behave like bulk silicon.

In order to characterize the structure of the films at thicknesses comparable to p-layer thicknesses in operational devices, we deposited 150Å thick films and determined their crystallinity. Deposition times for these films were estimated from the deposition rates measured on thicker films on SnO<sub>2</sub> substrates prepared under identical conditions. Raman analysis of the films showed that on SnO<sub>2</sub>-coated substrates the films had all amorphous character. On glass substrates, however, substantial crystalline fractions were observed. Considering the fact that deposition rates on glass substrates are generally lower than on SnO<sub>2</sub>, the data indicate that on glass substrates c-Si phase forms at film thicknesses considerably less than 150Å. It can then be concluded that lack of crystallinity on SnO<sub>2</sub> coated substrates is not simply due to the small film thickness.

To substantiate this observation we deposited the same films on the same substrates but coated *in-situ* with a very thin ( $\approx$ 10 Å) SiO<sub>x</sub> layer. Raman spectroscopic analysis of the films indicates the presence of c-Si phase in all cases but with a smaller c-Si peak width than for the films deposited on glass without SiO<sub>x</sub>. This could possibly indicate that SiO<sub>x</sub> film thickness was thick enough to provide a base for c-Si nucleation but not thick enough to suppress totally the effect of the underlying substrate.

#### Microcrystalline n-layers

A limited investigation of the microcrystalline n-layers deposited from SiH<sub>4</sub>, H<sub>2</sub>, and CO<sub>2</sub> found that they contained P doped c-Si imbedded in a matrix of a-SiO<sub>x</sub>:H:C. The c-Si volume fractions and conductivities are higher than what is observed in the B doped microcrystalline p-layers.

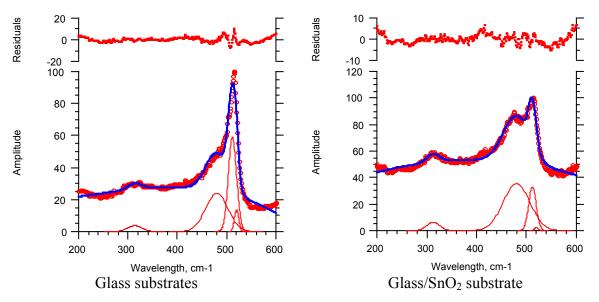

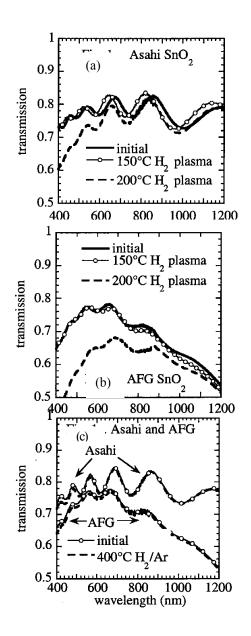

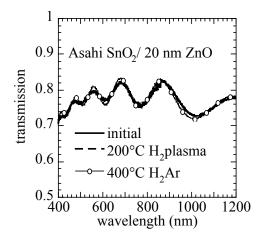

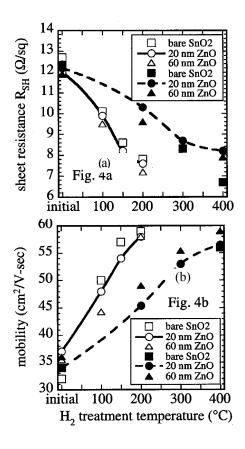

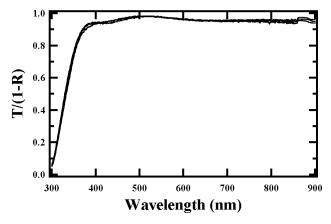

The sensitivity of three commercially available textured  $SnO_2$  substrate materials to  $H_2$  plasma or annealing in  $H_2/Ar$  from  $100\text{-}400^\circ C$  was investigated using optical transmission and Hall effect measurements. With both types of  $H_2$  treatments, the mobility of the  $SnO_2$  having the lowest carrier density ( $<2 \times 10^{20} \text{ cm}^{-3}$ ) doubles from  $\sim 30 \text{ to} \sim 60 \text{ cm}^2/V\text{-s}$  while the mobilities of  $SnO_2$  materials having a higher carrier density were unaffected. There was no systematic change in carrier density with either treatment for any  $SnO_2$ . The visible transmission degrades significantly with  $H_2$  plasma at  $200^\circ C$ , but it is unaffected by  $H_2/Ar$  annealing up to  $400^\circ C$ . Thus, it is possible to decrease the resistivity of bare  $SnO_2$  by a factor of 2 without any loss of transmission using  $H_2/Ar$  annealing. A 20 nm layer of sputtered ZnO is sufficient to protect the

$SnO_2$  from plasma-induced damage while still allowing the factor of two improvements in  $SnO_2$  mobility. Annealing in  $H_2/Ar$  or Ar is comparable and more effective than air, showing that there is both a chemical and thermal component to the improvement in mobility.

Minimizing the resistance between the p-layer and TCO of superstrate p-i-n a-Si devices and modules is a critical issue for utilizing new TCO materials like ZnO and new p-layers like μc-SiC or μc-SiO. However, characterization of the TCO/p interface is difficult since it is in series with the dominant p-i-n junction. We have developed two new methods to characterize the TCO/p contact and the SnO<sub>2</sub> sheet resistance in a completed device structure. Both require a-Si devices deposited on scribed TCO having individual cell contacts placed on each TCO strip. These methods were applied to devices made at BP Solar on different types of SnO<sub>2</sub> (Asahi, AFG, and LOF), different p-layer recipes, and with a thin ZnO layer on the SnO<sub>2</sub>. The junction and contact properties are obtained from analysis of dV/dJ from each of several devices on the strip of TCO. Analysis of temperature dependent JV measurements using this special configuration can be used to determine the activation energy of the TCO/p contact resistance.

There was no significant difference in  $R_{TCO/P}$  between  $SnO_2$  or ZnO substrates, or with  $H_2$  plasma treatments. The reason for poor  $V_{oc}$  and FF with ZnO must be found elsewhere. Instead, our analysis showed that the diode factor and recombination current increases with ZnO, especially with certain pre-deposition treatments.

A unique feature of these methods is the direct measurement of the JV characteristic of the TCO/p contact. No evidence for a blocking contact, a photovoltaic junction or a high resistance was found. Instead, ZnO changes the p/i junction recombination. Values of the contact resistance (R<sub>C</sub>) of 1  $\pm$  0.5  $\Omega$ -cm² were found for a wide range of TCO and p-layer processing, including ZnO. Temperature dependence of R<sub>C</sub> gave barrier height of 40-55 meV. Analysis of devices with a thin ZnO layer on SnO<sub>2</sub> and with different predeposition treatments indicates lower V<sub>oc</sub>, and FF observed with ZnO is not due to the contact but to changes in the p/i junction recombination. The solar cell performance is very sensitive to the ZnO surface treatment, but R<sub>C</sub> is not. No evidence was found for a blocking or high resistance ZnO/p contact. The "ZnO/p" contact problem is not really due to the ZnO/p contact resistance or a barrier but rather to an increase in recombination.

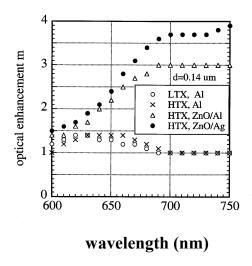

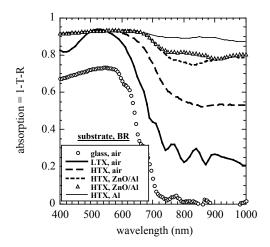

Optical enhancement in a-Si solar cells is a well-known technique to increase the absorption efficiency of weakly absorbed light, and is critical for improving the performance of single or multijunction p-i-n or n-i-p devices. Optical enhancement increases the optical path length so that the device has an effective optical thickness of (*m*d) where d is the physical thickness of the i-layer. The parameter *m* represents the increase in absorption length and is a measure of the optical enhancement for weakly absorbed light due to both oblique scattering and multiple passes. We have developed a quantitative analysis of the QE and applied it to a wide range of a-Si p-i-n solar cell device structures. The measured QE data at long wavelengths is fit with a simple, analytical model having one adjusted parameter, *m*, as a function of wavelength. The experimental variables investigated include the i-layer thickness, d, from 0.14 to 0.92 µm, the SnO<sub>2</sub> texture (lightly textured LTX or highly textured HTX), and the back reflector (BR) structure (Al, ZnO/Al, or ZnO/AG).

Values of m are generally less than 1.5 with Al contacts on the LTX or HTX substrates for all device thicknesses studied here. This indicates a strong reduction in multiple passes due to the Al BR regardless of how textured the  $SnO_2$  is. But m increases significantly with ZnO/metal contacts on HTX  $SnO_2$ , saturating at  $m \sim 3$  - 4. We found that the ZnO/Ag BR enhances light trapping more in thin devices compared to thicker ones. These results confirm the critical importance of a ZnO (or any other TCO buffer layer) between the Si and metal layers for improving optical enhancement of the QE. Besides gains in QE due to optical enhancement, we also considered the losses due to parasitic absorption. By comparing absorption in different simplified test structures with and without back reflectors, we conclude that the textured  $SnO_2$  is responsible for a very significant fraction of the parasitical absorption. Absorption of about  $SnO_2$  of the light is unaccounted for beyond  $SnO_2$  must the HTX  $SnO_2$ . The most likely parasitic loss, as at long wavelengths, is light absorbed in the textured  $SnO_2$ . Critical angle trapping inside the  $SnO_2$  will lead to multiple internal reflections or light piping in the  $SnO_2$ . This suggests that in a solar cell, light that is reflected from the BR but not absorbed in the i-layer can be trapped in the  $SnO_2$ , remaining there instead of re-entering the i-layer.

The hot-wire CVD of uniform Si films onto 1 in<sup>2</sup> 7059 glass substrates was investigated. We studied the effects of silane flow rate (4-60 sccm), filament temperature (1550-1850°C), total pressure (25-1000 mTorr), substrate temperature (400-600°C) and hydrogen dilution on the exit gas-phase composition, film growth rate and film crystalline fraction. Experiments show that the growth rate increases with silane flow rate and is independent of substrate temperature. The growth rate variation with pressure and filament temperature is observed to change with the axial position of the substrates. A transition from amorphous to polycrystalline silicon films is observed with increasing total pressure, filament temperature and substrate temperature, and with decreasing silane flow rate. The effect of hydrogen dilution is found to be equivalent to the effect of increasing gas pressure using pure silane.

To explain these results, a quantitative model of the deposition of silicon films by HWCVD was developed. The model equations describe a vacuum reactor in which silane cracks over a series of heated tantalum wire reacts further in the gas phase and deposits to form Si films on glass substrates. The model considers gas motion in the form of diffusion in the reactor and incorporates surface pyrolysis reactions on the hot wire, gas-phase reactions, and film growth reactions on the substrates. The model predictions of silane conversion and silicon film growth rate are in good agreement with the experimental results over the range of conditions studied. This study shows that a critical ratio of atomic hydrogen flux relative to the total flux of growth precursors is required at the film surface in order to effect a transition from amorphous to polycrystalline silicon films. The flux ratio of atomic hydrogen radical to growth precursors is controlled by the pressure, filament temperature and silane flow rate. For the conditions investigated, a flux ratio greater than 15 leads to the deposition of polycrystalline silicon films.

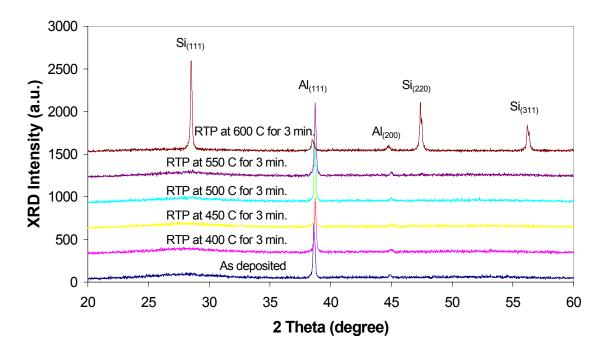

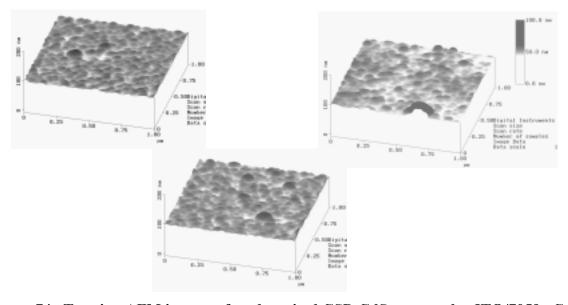

One of the critical issues in the development of thin film silicon devices is the grain size. Typically, films deposited by HWCVD exhibit grain sizes between 10-50 nm. It is expected that the excessive number of grain boundaries in such films will lead to considerable carrier recombination and poor device performance. During this contract, we have focused on the evaluation of various *in-situ* and post-treatment methods, which can be used to fabricate films with micrometer size grains. The core idea in all these approaches is the process of metal induced crystallization (MIC) by which a-Si undergoes crystallization when in contact with

metals such as Al, Ni and Sb at temperatures as low as 200°C. In one approach, we investigated the use of RTP MIC in collaboration with Ajeet Rohatgi at Georgia Institute of Technology. Although only preliminary, results in this study do not show grain enhancement in the films. We have also investigated the use of *in-situ* approaches, which leads to grain enhancement during the HWCVD process. The work has concentrated on the use of Al and Sb layers as the catalysts for grain enhancement and crystallization. We have studied two temperature regimes, i.e., temperatures above and below the Al-Si eutectic temperature 575°C. In the first case, films have a tendency to delaminate from the substrate. This is caused by poor wetting characteristics of the metal layer on the glass substrate at the processing temperature. For the lower temperature regimen, uniform films have been obtained. These films do not contain Al contamination and have a columnar structure with a diameter in the micrometer range. Characterization after polishing to reveal grain boundaries indicates the grains have a micrometer size width as far as the interface with the Al layer.

#### Si Team Participation

IEC is a member of the National a-Si Team under the Thin Film Partnership Program. Steve Hegedus had been the leader of the Multijunction Device sub-team for 8 years and stepped aside last year. The work on characterization of the TCO/p contact resistance was performed as part of the Teaming activities in collaboration with BP Solarex. Results from this work have lead BP Solarex to develop new TCO/p materials and processes. During this contract period, IEC collaborated with: Gautam Ganguly at Solarex, by characterizing the TCO/p contact resistance on their sub-modules having different textured SnO<sub>2</sub>; Bhushan Sopori at NREL, by fabricating back reflector structures on textured TCO/a-Si substrates for analysis by PVOPTICS; Prof. Roy Gordon at Harvard University, by characterizing ZnO films deposited there by APCVD and fabricating a-Si pin devices on those films for comparison to standard SnO<sub>2</sub> substrates; and Prof. Eric Schiff at Syracuse University, by providing him with special TCO/i-n device structures for electroabsorption measurements. These teaming collaborations lead to co-authoring one publication at the Spring 2000 Materials Research Society Conference and two at the 28<sup>th</sup> IEEE Photovoltaic Specialists Conference.

#### CdTe-BASED SOLAR CELLS

CdTe-CdS Interdiffusion and Post-Deposition Processing

Chemical and kinetic aspects of thin-film CdTe/CdS solar cell processing have been analyzed and provide a framework for variation and failure analysis and control of large-area cells in modules. In particular, controlling CdS thickness and CdTe grain properties during growth or post-deposition treatments will become more critical as CdS and CdTe film thickness are reduced; the analysis shows that 'tolerant' processing windows exist for fabricating efficient cells in the low-limit of semiconductor film thickness.

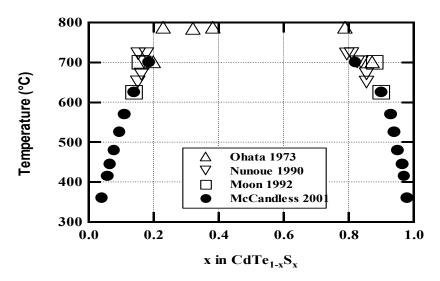

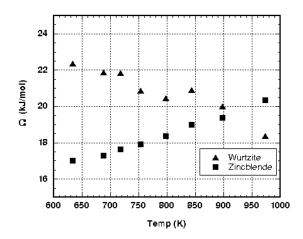

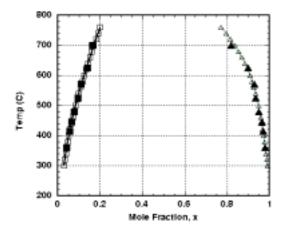

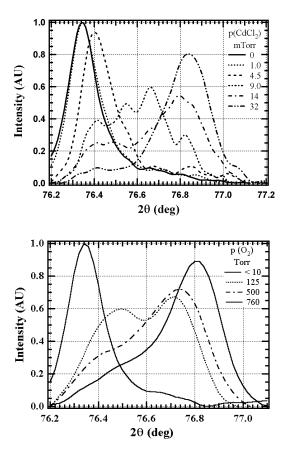

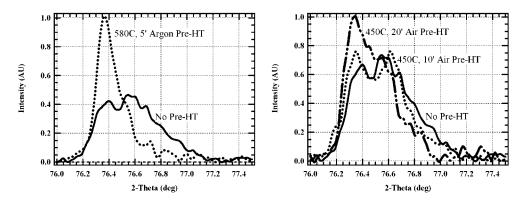

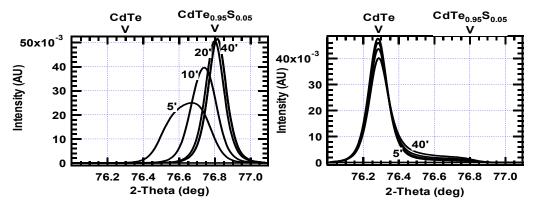

The CdTe-CdS phase system has been quantitatively analyzed in thin-film structures and has been shown to conform to the equilibrium system for CdTe-CdS mixed crystals. The miscibility gap for the CdTe-CdS pseudobinary system was investigated in the temperature range used to process thin-film solar cells, i.e., from 360°C to 700°C. Metastable single-phase CdTe<sub>1-x</sub>S<sub>x</sub> alloy thin films with composition near the middle of the alloy range, x~0.4, were deposited by thermal

evaporation. Thermal treatment in a kinetically enhancing ambient resulted in segregation of the equilibrium alloy phases. Analysis of the resulting x-ray diffraction patterns yielded precision lattice parameters, hence composition, of the Te-rich zincblende and S-rich wurtzite phases. The *T-x* phase boundaries were found to be asymmetrical and were modeled using non-ideal solution thermodynamics. The empirical and modeled phase boundaries provide the fundamental basis for investigation of interdiffusion between CdTe and CdS.

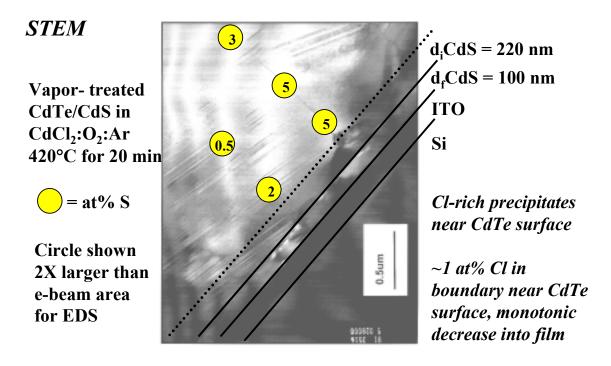

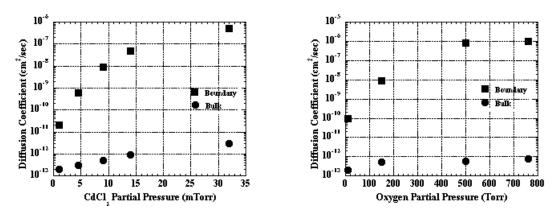

Analysis of superstrate and substrate CdTe/CdS structures with CdTe deposited at low temperatures has allowed chemical and thermal effects to be de-coupled. The effects of the observed phenomena on thin-film polycrystalline CdTe/CdS device operation can be summarized as follows. CdS diffusion into CdTe reduces the CdTe bandgap slightly, lowering the built-in voltage. This is offset by a slight increase in long wavelength quantum efficiency. CdS thickness is reduced, which increases light generated current due to greater absorption of short wavelength photons in CdTe. However, non-uniform CdS consumption can lead to poor overall junction behavior by the formation of a sufficient number of parallel junctions between CdTe/TCO and CdTe/CdS. This problem can be ameliorated by modifying the CdS growth habit and introducing high resistance oxide layers between CdS and the TCO. The effect of bandgap variations parallel to the junction interface is still not understood.

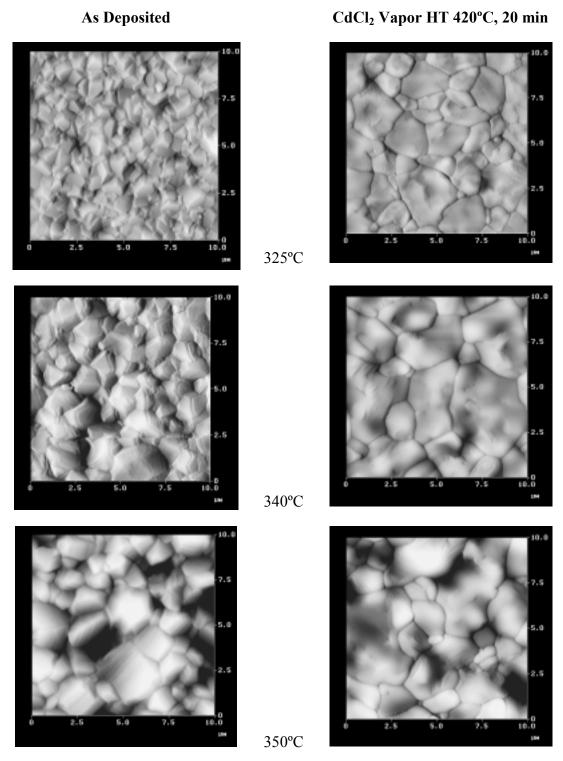

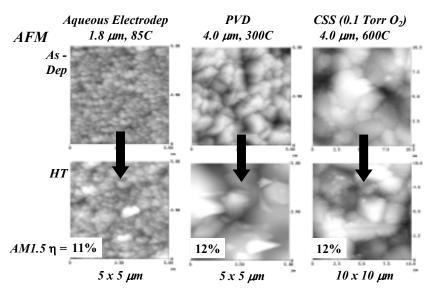

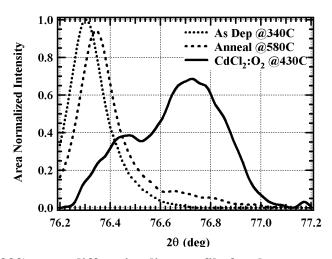

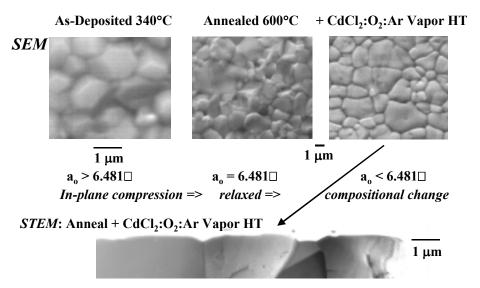

By comparing films deposited by different techniques used to obtain solar cell efficiencies in the 11 to 12% efficiency range, it is shown that film morphology per se is not an efficiency-limiting parameter for films with grains from 0.2 to < 2 microns in lateral dimension. We have shown that in PVD films, the CdCl<sub>2</sub> treatment causes grain growth by a coalescence process. However, it seems that devices with CdTe films having sub-micron grains can benefit from the growth of penetrating oxides which electrically passivate grain boundaries and kinetically reduce CdS consumption during treatment with CdCl<sub>2</sub> and O<sub>2</sub>. High conversion efficiencies are still restricted to cells with CdTe deposited by CSS in oxygen-containing ambient. A negative consequence of oxide formation on the CdTe surface is the need for aggressive chemical treatments to allow low resistance contacts to be formed. Residual oxygen in grain boundaries may play a significant role in controlling grain boundary diffusion of contact-related species such as contaminants and dopants. The dependence of the limiting diffusivities for CdS diffusion into CdTe on temperature and ambient composition in thin-film couples have been determined, yielding activation energies for bulk and grain boundary diffusion processes. The bulk diffusion appears to be limited by the Cd self-diffusion, while the boundary diffusion is chemically limited. Intra-grain recrystallization proceeds more rapidly than grain growth, which proceeds more rapidly than CdS diffusion, even in films without oxides. The observed benefit of high temperature growth or high temperature anneal strongly suggests that grain quality is of paramount importance to obtaining high junction quality.

#### **Window Layer Processing**

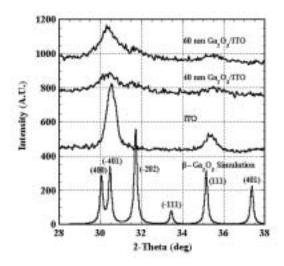

Options for window layer processing were evaluated, with emphasis on development of high resistance transparent (HRT) oxide layers and improved CdS film quality. Resistive oxide  $SnO_2$ ,  $In_2O_3$ , and  $Ga_2O_3$  films were formed by oxidizing metal films, Sn, In, and Ga, respectively, in air at  $400^{\circ}C$ - $500^{\circ}C$ . Incorporation of these layers between the TCO and the CdS film allows junction quality to be similarly maintained for devices with d(CdS) < 100 nm.

A new method for chemically depositing CdS films with very high utilization of cadmium species was developed and has been submitted for patent review. The method, called chemical surface deposition (CSD), yields conformal CdS films with >70% cadmium utilization and low pinhole and particulate occurrence, contributing to process robustness. It was also demonstrated that CSD  $Cd_{1-x}Zn_xS$  films may be used in lieu of a CdS/HR combination to simplify processing and retain junction quality while obtaining high photocurrent.

#### **Contact Processing and Stress Analysis**

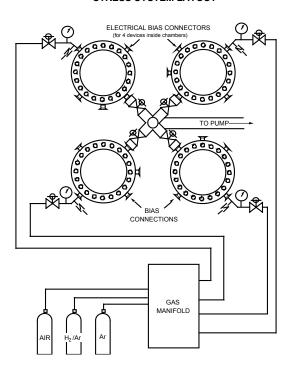

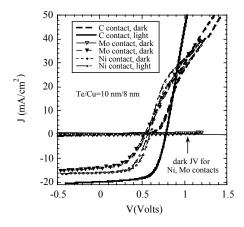

At the beginning of this contract, it was already well established that the contacting of CdTe is problematic and the details of the contact were crucial to obtaining a high performance device. There were suggestions that the contact process and structure can influence the stability under accelerated stress conditions and that the electrical bias during stress was important to understanding the degradation. Therefore, we established a contact fabrication process which allowed us to separate and control various aspects of the contact process, such as removing oxides on the CdTe surface, formation of the Te layer, applying Cu and reacting it to form Cu-Te alloys, and forming a robust current carrying contact. We separated these features into the primary and secondary contacts. The primary contact may contain Cu-Te alloys and makes intimate contact to the CdTe. The secondary contact is typically a thick layer of C, Mo, Ni or Al and carries the current to the external connections. We also built a system for accelerated stressing of thin film PV devices under controlled atmosphere, temperature, bias, and light conditions, and used it to stress a large number of CdTe devices with a variety of contact structures. The glass/SnO<sub>2</sub>/CdS/CdTe plates for these contacting and stress studies were obtained from First Solar, L.L.C.. The CdS and CdTe were evaporated. The 4 µm thick CdTe received a CdCl<sub>2</sub> treatment at First Solar. Thus, devices were fabricated using CdS/CdTe material from First Solar with back contact processing at IEC. Given the well known sensitivity of CdTe device performance and degradation to the back contact, these results on hybrid FS/IEC devices do not quantitatively reflect the behavior of First Solar devices with their own contact process.

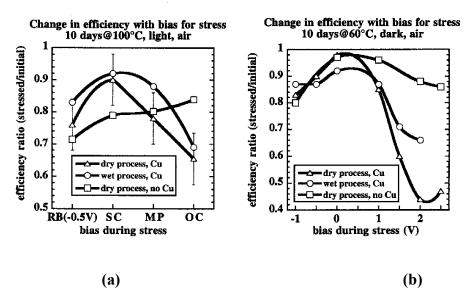

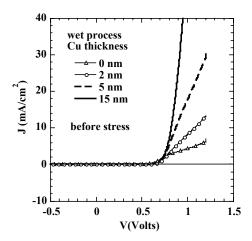

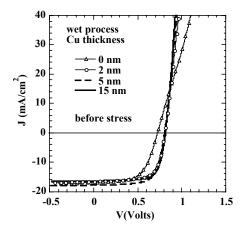

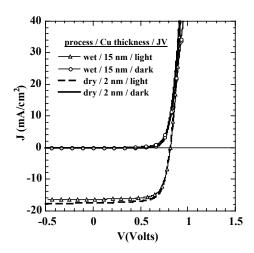

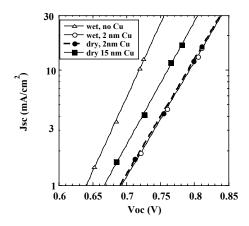

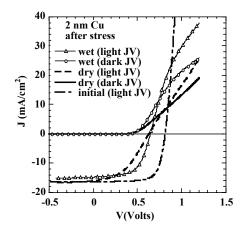

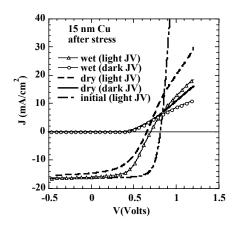

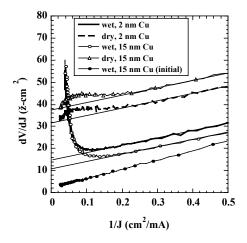

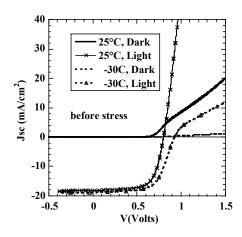

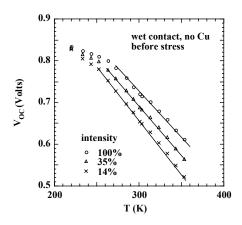

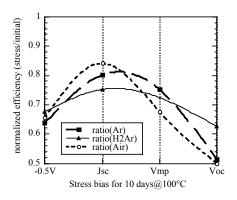

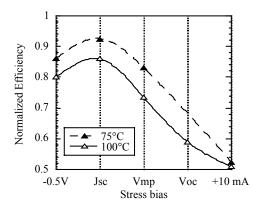

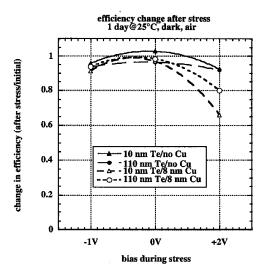

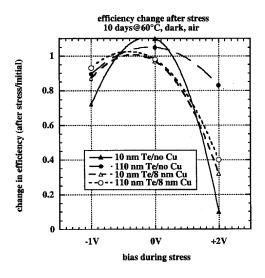

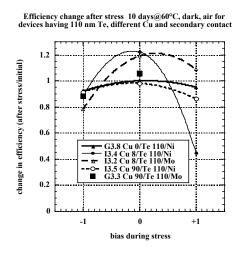

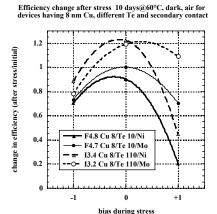

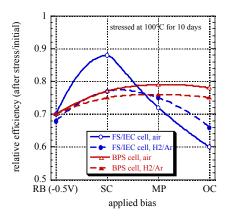

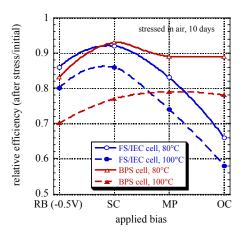

CdTe cells have been stressed for 10-30 days at  $60\text{-}100^{\circ}\text{C}$  under  $\sim 1$  sun light and in dark. Ambient conditions have included dry (bottled) air,  $H_2/Ar$  and Ar. Of critical importance is the bias applied to the cell during stress. Various bias points have been studied: short circuit (SC), maximum power (MP), open circuit (OC) as well as -1V and +2V. Variations in cell processing has included the Cu thickness (0-15 nm), wet or dry surface treatment, various secondary contacts (C paste, Ni, and Mo). In general, we focused on the effect of bias during stress and the effect of the contact process on initial and post-stress performance. A variety of JV analysis methods were applied to gain further insight into device mechanisms in the initial and degraded states.

We have shown that devices degrade in both illumination and dark conditions during stress, and even at temperatures as low as 60°C. Devices biased at SC, or 0V in the dark, were more stable than those at forward or reverse bias. This highlights a crucial observation which must be accounted for in developing a model, namely that the degradation is non-monotonic with bias. Degradation increases with increasing forward bias, at least up to 2.5V. Devices without Cu degrade much less, especially at forward bias. There is little difference between devices where the pre-contact treatment of the CdTe was a wet or dry process, providing that the Cu thickness

was optimized for each process. Considerable variability has been found for nominally similar devices under similar stress conditions. Devices stressed at 0V for 10 days at 100°C can degrade as little as 2-3% or as much as 20%. Given the excellent control over the stress conditions, we attribute the variability to unintentional differences in the CdS/CdTe starting material or the lack of reoptimization of the contact for different starting material properties.

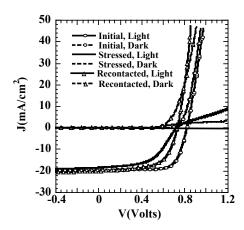

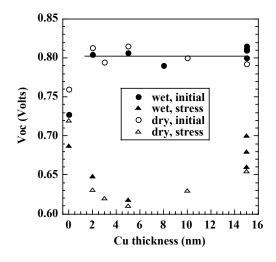

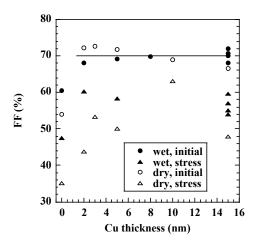

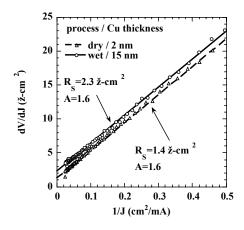

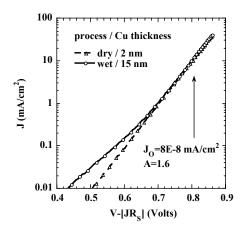

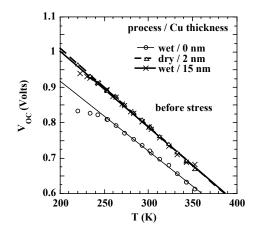

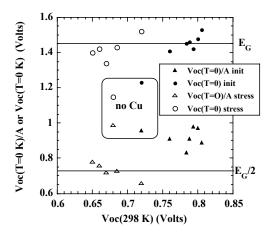

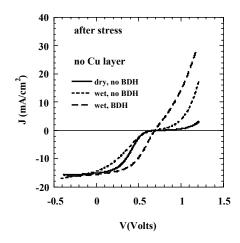

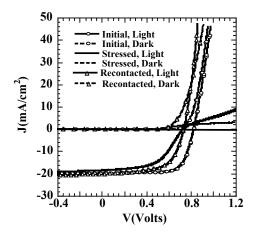

Initial performance is very similar for devices with the wet or dry surface process, independent of Cu thickness. Initial  $V_{oc}$  was  $0.80\pm0.02~V$  and initial FF was  $69\pm2\%$  for all devices except ones without Cu. After stress, devices without Cu having the wet contact have higher  $V_{oc}$  than devices with Cu, despite starting with a lower initial  $V_{oc}$ . But we found no strong dependence of either solar cell performance ( $V_{oc}$ , FF,  $J_{sc}$ ) or device properties (A,  $J_{o}$ , space charge,  $R_{s}$ ) on Cu concentration (2-15 nm) or the contact process. These results demonstrate significant degradation occurs independent of the amount of Cu for both of the contact processes. Although we observed that devices with the dry contact process tend to have less "roll over" or curvature in forward bias after stressing, they had no significant difference in FF. This suggests the wet contact enhanced the formation of the blocking contact despite its having consistently a slightly higher FF after stress. The two key differences between the dry and wet process are that the dry process leaves a thinner Te layer and is less penetrating along grain boundaries. It is not known yet how these differences are responsible for the differences in blocking contact formation.

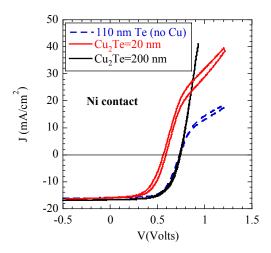

The effect of the secondary contact was unexpectedly large. Mo and Ni required thicker Te layers (110 nm vs 10 nm) to achieve even moderate device performance. Thicker Te was collarated with better intial and degraded performance with all secondary contacts. Devices with C have higher initial  $J_{sc}$  and  $V_{oc}$  compared to devices with Mo or Ni. We have no explanation for this. All three secondary contacts were relatively stable without a Cu layer.

Analysis of the J(V) characteristics indicates that the junction recombination is a Schockley-Read-Hall (SRH) mechanism. Evidence includes A values between 1.5 and 2.0,  $V_{oc}(T)$  values extrapolated to T=0K equal to the CdTe bandgap, and the temperature dependence of  $J_o$  giving an activation energy near mid-gap of CdTe. This suggests that deep centers in the CdTe, whose concentration increases with stress are responsible for the recombination limiting  $V_{oc}$ .

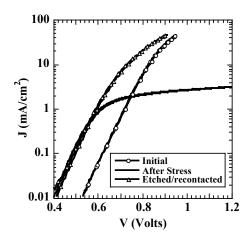

Losses in  $V_{oc}$  and FF occur within the ~1 week stress time used in this study while stressing for longer times enhances the formation of the blocking contact. We developed a method to recontact devices after stress, and found that losses in  $V_{oc}$  and FF are independent and separable. Recontacting cells after stress may eliminate the roll-over and partially recover some of the FF loss but there is no recovery in  $V_{oc}$ .

Since even devices without any Cu layer show degradation, other non-Cu related degradation mechanisms must be identified and solved. Before stressing, low  $V_{oc}$  and FF result without Cu doping layer, consistent with our previous results using both SCI/FS CdTe material. Degradation in  $V_{oc}$  for these "Cu free" devices is much less ( $\sim 0.06~V$ ) than typically found for devices with Cu layer. The relatively smaller loss in  $V_{oc}$  after stressing is independent of the contact processing or surface etch. However, severe degradation in FF occurs even without Cu. Devices without the BDH etch show extreme distortion of the JV curve, suggesting formation of a blocking contact is suppressed with sufficient Cu or Te, consistent with maintaining a p+ surface. The changes in J-V behavior due to stress suggest changes in non-copper doping

sources such as oxygen, chlorine, and excess Te. Devices with insufficient Cu dopant will be more susceptible to presence of other doping species, which may be less well controlled.

We collaborated extensively with First Solar LLC, who provided most of the bare CdS/CdTe plates on which contact and stress analyses were conducted. Extensive collaborations were also conducted with BP Solar with respect to film morphology, structure and chemical composition. We performed stresses on their own completed devices to determine temperature and ambient dependence as well as assist them in evaluating stability of different back contact processes. In general, we found no dependence of stability on the ambient (air, H<sub>2</sub>.Ar, or Ar). We found some dependence on temperature, with degradation increasing as the stress temperature increased from 60 to 100°C.

#### **Teaming Activity**

IEC researchers participated in the National CdTe R&D Team, attended and made presentations at team meetings. Collaborations within the team activity consisted of device fabrication, device stressing, performing electrical and physical characterization of films and devices, and exchange of technical progress. In addition, thin-film samples were provided to various team members. IEC participated in the First Solar focus group and provided film characterization, device analysis, and interpretation of SIMS measurements made at NREL. Direct interaction between IEC and BP Solar yielded a fruitful collaboration in which processing developments at IEC such as post-deposition treatments and incorporation of HR layers were successfully incorporated into the Apollo line, resulting in significant performance gains.

#### TRAINING AND EDUCATION

During the period of this subcontract (August 24, 1998 to October 23, 2001) IEC provided training and education for the following: 10 visiting professionals; 11 post-doctoral fellows/limited term researchers; 18 graduate students; and 16 undergraduate students. Names are given in the list of contributors.

#### **PUBLICATIONS**

As a result of research performed under this subcontract reporting period, IEC published 34 papers, as shown in Appendix 1.

#### ORGANIZATION OF THE REPORT

This report is organized into three technical sections: CuInSe<sub>2</sub>-based solar cells, Si-based solar cells, and CdTe-based solar cells. Each section describes the progress made at IEC in addressing the critical issues discussed above during the period of this subcontract.

#### LIST OF CONTRIBUTORS

#### PRINCIPAL INVESTIGATORS

Roger Aparicio Robert W. Birkmire Kevin Dobson Erten Eser Steven S. Hegedus Brian E. McCandless James E. Phillips T.W. Fraser Russell William N. Shafarman

#### RESEARCHERS

Wayne A. Buchanan Marylin Huff

#### VISITING PROFESSIONALS

Nto Diarra, Visiting Scholar, University of Lowell, Massachusetts

Dirk Hofmann, Visiting Scholar, University of Stuttgart, Germany

Josef Kallo, Visiting Scholar, University of Stuttgart, Germany

Ruhi Kaplan, Fulbright Scholar, University of Erciyes, Turkey

Donghwan Kim, Visiting Scientist, Korea University, Seoul, Korea

Sylvain Marsillac, Visiting Scholar, Universite de Nantes, France

Julius Mwabora, Fulbright Fellow, University of Dar-es-Salaam, Tanzania

Hans-Werner Schock, Visiting Scientist, University of Stuttgart, Germany

Issakha Youm, Fulbright Scholar, Cheikh Anta DIOP University, Senegal, West Africa

Xiangbo Zeng, Visiting Scholar, Liaoning Normal University, Liaoning Province, China

#### POST-DOCTORAL FELLOWS/LIMITED TERM RESEARCHER

Mario Gossla

Eric Gourmelon

Greg Hanket

Sukti Hazra

Michael Maldei

Sylvain Marsillac

Takashi Minemoto

Devassey Paulson

Baosheng Sang

Udai Singh

Jie Zhu

#### TECHNICAL SUPPORT

Charles Debo

Vicky DiNetta

Ronald Dozier

Shannon Fields

**Dmitriy Gusakov**

Kevin Hart

Tom Hughes-Lampros

Herbert Wardell

#### **GRADUATE STUDENTS**

Joy Deep Dass

Jeff Doody

Sunil Earath

Ozgenc Ebil

Michael Engelmann

Moses Haimbodi

Rajesh Hiranandani

Toby Junker

Jim Kleisch

Niu Jin

Wei Liu

Chao Ying Ni

Atul Pant

Jochen Titus

Qian Xie

Zhao-Hui Yang

Dan Zak

Mike Zellner

#### **STUDENTS**

Brian Atkinson

Jason Baxter

George Brown

Josh Cadoret

Rosa Calderon

Daniel Eichenwald

Jonathan Frey

Michael Gibson

Tom Gillis

Dana Kolesar

Timothy Miller

Alpa Modi

Chintan Mody

John Ritter Daniel Ryan Alexis Siery

# DOCUMENT PREPARATION

Steven S. Hegedus Linda Granger

# **TABLE OF CONTENTS**

| SU  | MM/   | ARY    |                                                                                       | i       |

|-----|-------|--------|---------------------------------------------------------------------------------------|---------|

| LIS | T OI  | F CON  | TRIBUTORS                                                                             | xiv     |

| TA  | BLE   | OF CO  | ONTENTS                                                                               | xvii    |

| LIS | ST OI | F FIGU | RES                                                                                   | . xx    |

|     |       |        | _ESx                                                                                  |         |

|     | ,, ,, | IADI   |                                                                                       | A V I I |

| 1.  | INTE  | RODUC  | CTION                                                                                 | 1       |

|     |       |        | Se <sub>2</sub> -based Solar Cells                                                    |         |

|     |       |        | I-based Solar Cells                                                                   |         |

|     | 1.3   |        | -based Solar Cells                                                                    |         |

| 2.  | Culr  | ոՏe₂-B | ASED SOLAR CELLS                                                                      | 3       |

|     | 2.1   | Effect | of Deposition Temperature on Cu(InGa)Se <sub>2</sub> Films and Devices                | 3       |

|     |       |        | Introduction                                                                          |         |

|     |       | 2.1.2  | Experimental Details                                                                  | 3       |

|     |       | 2.1.3  | Results                                                                               | 5       |

|     |       | 2.1.4  | Cu(InGa)Se2 Deposition with In-Ga-Se Nucleation Layer                                 | . 13    |

|     |       |        | Discussion And Conclusions                                                            |         |

|     | 2.2   | Depos  | sition of Cu(InGa)Se₂ Films by In-Line Evaporation                                    | . 14    |

|     |       |        | Introduction                                                                          |         |

|     | 2.3   | Form   | ation and analysis of Graded Culn(SeS) $_{2}$ and CuGa(SeS) $_{2}$ Films              | . 23    |

| 3.  | Si-B  |        | SOLAR CELLS                                                                           |         |

|     | 3.1   | Micro  | crystalline Silicon Carbide p-layers                                                  | . 24    |

|     |       |        | Introduction                                                                          |         |

|     |       |        | Experimental Approach                                                                 |         |

|     |       |        | Results and Discussion                                                                |         |

|     | 3.2   | Micro  | crystalline Silicon Oxide p-layers                                                    | . 29    |

|     |       |        | Effect of Substrates                                                                  |         |

|     |       |        | SIMS Analysis                                                                         |         |

|     |       | 3.2.3  | Effect of Diborane Level in Discharge                                                 | . 30    |

|     |       |        | Effect of Hydrogen Dilution                                                           |         |

|     |       |        | Crystallization in Ultra-thin Films                                                   |         |

|     |       |        | Conclusions Regarding Silicon Oxide p-layers                                          |         |

|     | 3.3   | Micro  | crystalline silicon oxide n-layers                                                    | . 33    |

|     | 3.4   | Effect | of H <sub>2</sub> Treatments on Optical and Electronic Properties of SnO <sub>2</sub> |         |

|     |       |        | trates Used for a-Si Solar Cells                                                      |         |

|     |       |        | Background                                                                            |         |

|     |       |        | Experimental Techniques                                                               |         |

|     |       |        | Results                                                                               |         |

|     |       | 3.4.4  | Discussion                                                                            | .43     |

|    | 3.5 | Characterization of the SnO <sub>2</sub> /p and ZnO/p Contact Resistance and Junction Properties in a-Si p-I-n Solar Cells and Modules    | 15  |

|----|-----|-------------------------------------------------------------------------------------------------------------------------------------------|-----|

|    | 3.6 | Analysis of QE to Determine Optical Enhancement                                                                                           |     |

|    | 3.7 | HWCVD of Silicon Films and Reactor/Reaction Analysis and Modeling                                                                         |     |

|    | •   | HWCVD                                                                                                                                     | _   |

|    | 3.8 | Grain Enhancement of HWCVD Films                                                                                                          | 50  |

|    |     | 3.8.1 Post-Deposition Grain Enhancement of HWCVD Si Films                                                                                 |     |

|    |     | 3.8.2 In-situ Grain Enhancement of HWCVD Films                                                                                            | 54  |

| 4. | CdT | e-BASED SOLAR CELLS                                                                                                                       | 62  |

|    |     | CdTe-CdS Interdiffusion                                                                                                                   |     |

|    |     | 4.1.1 Introduction                                                                                                                        | 62  |

|    |     | 4.1.2 Approach                                                                                                                            | 63  |

|    |     | 4.1.3 Results                                                                                                                             |     |

|    |     | 4.1.4 Summary and Conclusions                                                                                                             |     |

|    | 4.2 | Window Layer Processing                                                                                                                   |     |

|    |     | 4.2.1 Introduction                                                                                                                        |     |

|    |     | 4.2.2 Experimental Approach                                                                                                               |     |

|    |     | 4.2.3 Results                                                                                                                             |     |

|    |     | 4.2.4 Summary and Conclusions                                                                                                             |     |

|    | 4.3 | Contacts and Accelerated Stressing                                                                                                        |     |

|    |     | 4.3.1 Introduction                                                                                                                        |     |

|    |     | 4.3.2 Contacting (Wet, Dry, Primary, Secondary, Cu-Te Formation)                                                                          |     |

|    |     | <ul><li>4.3.3 System for Accelerated Stress Studies</li><li>4.3.4 Stress of Partially Completed Devices and Recontacted Devices</li></ul> |     |

|    |     | 4.3.5 Effect of Wet vs Dry Process, and Cu Thickness (OC stress, 100°C                                                                    |     |

|    |     | 4.3.6 Effect of temperature, bias and ambient during stress                                                                               | ,   |

|    |     | 4.3.7 Separating the Effect of Primary and Secondary Contacts                                                                             |     |

|    |     | 4.3.8 Effect of Temperature and Ambient                                                                                                   |     |

|    |     | 4.3.9 Recovery After Accelerated Degradation                                                                                              |     |

|    |     | 4.3.10 Summary and Conclusions                                                                                                            |     |

| 5  | ΔRS | STRACT                                                                                                                                    |     |

| ٥. |     |                                                                                                                                           | 100 |

|    |     |                                                                                                                                           |     |

# **LIST OF FIGURES**

| Figure 1. Schematic representation of three temporal flux profiles (a) and integrated relative Cu concentration in films (b) during deposition with different Cu(InGa)Se <sub>2</sub> evaporation flux sequences                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2. Compositional ratios $Cu/(In+Ga)$ and $Ga/(In+Ga)$ determined from AES depth profiles for films deposited at $T_{ss}=480^{\circ}C$ with, (a) Cu-rich flux in the beginning of the deposition, (b) Cu-rich flux in the middle of the deposition, and (c) uniform flux. |

| Figure 3. Cross-sectional SEM micrographs of $Cu(InGa)Se_2$ films deposited with different flux profiles at $T_{SS} = 400$ and $550^{\circ}C$                                                                                                                                   |

| Figure 4. AFM images showing 5 $\mu$ m x 5 $\mu$ m areas of films deposited with Cu-rich flux at $T_{SS}$ = 400, 480, and 550°C.                                                                                                                                                |

| Figure 5. AFM images of the top surface of films deposited with a Cu-rich flux at the beginning of the deposition. Each figure shows a 10 $\mu$ m x 10 $\mu$ m area                                                                                                             |

| Figure 6. Grain boundary maps created from the AFM images in Figure 59                                                                                                                                                                                                          |

| Figure 7. Grain size distributions for Cu(InGa)Se <sub>2</sub> films deposited with Cu-rich flux and log-normal fits to each distribution                                                                                                                                       |

| Figure 8. Sodium content measured by SIMS in $Cu(InGa)Se_2$ films deposited at $T_{SS} = 400$ and $550^{\circ}C$                                                                                                                                                                |

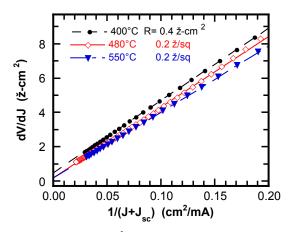

| Figure 9. Current-voltage curves for devices with Cu(InGa)Se <sub>2</sub> deposited at different T <sub>SS</sub> with Cu-rich growth at start                                                                                                                                   |

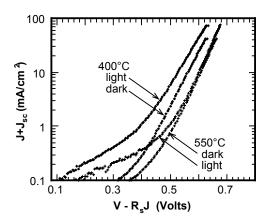

| Figure 10. Derivative vs. $(J+J_{SC})^{-1}$ of the data in Figure 9 used to determine                                                                                                                                                                                           |

| Figure 11. Logarithmic J-V behavior showing differences between light and dark curves for the 400°C case                                                                                                                                                                        |

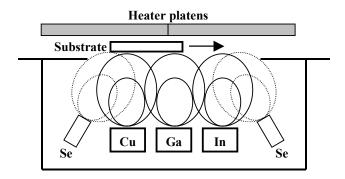

| Figure 12. Schematic of elemental in-line evaporation                                                                                                                                                                                                                           |

| Figure 13. IEC in-line evaporation system                                                                                                                                                                                                                                       |

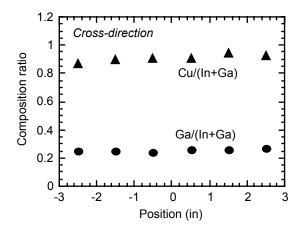

| Figure 14. Compositional uniformity across the deposition zone                                                                                                                                                                                                                  |

| Figure 15. AES depth profile of Cu(InGa)Se <sub>2</sub> film deposited at 525°C and 1"/min                                                                                                                                                                                      |

| Figure 16. Film composition with varying substrate transport speed                                                                                                                                                                                                              |

| Figure 17. Variables used in effusion analysis                                                                                                                                                                                                                                  |

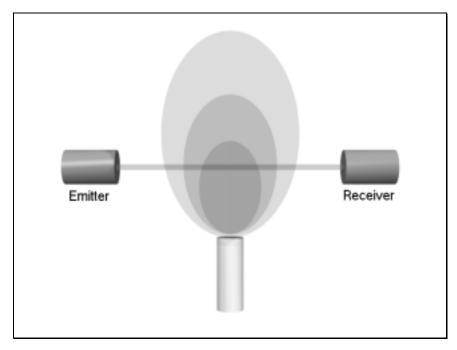

| Figure 18. Apparatus for measuring flux distribution from a nozzle                                                                                                                                                                                                              |

| Figure 19. Effusion profile of IEC in-line evaporation sources                                                                                                                                                                                                                  |

| Figure 20. Illustration of AA beam passing through the variable-density effusion profile of an evaporation source                                                                                                                                                               |

| Figure 21. Raman spectrum of a μc-Si film deposited with CH <sub>4</sub> normalized flow of 0.33                                                                                                                                                                                |

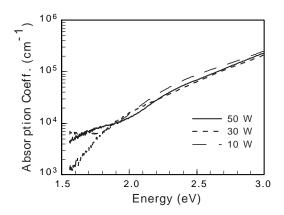

| Figure 22. c-Si volume fraction and dark conductivity as a function of discharge power.                                                                                                                                                                                                                                                                | 26 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 23. Absorption coefficient as a function of energy at three different discharge power levels.                                                                                                                                                                                                                                                   | 26 |

| Figure 24. Raman spectra of the films deposited c = 0.5 at a power density of 160 mW/cm <sup>2</sup> . The labels give hydrogen dilution levels.                                                                                                                                                                                                       | 28 |

| Figure 25. Raman spectra of the films from run #4847 deposited with CO <sub>2</sub> discharge on glass and glass/SnO <sub>2</sub>                                                                                                                                                                                                                      | 29 |

| Figure 26. SIMS depth profiles of the films from run 4847. Thinner lines are the film on glass while thicker lines are the film on SnO <sub>2</sub>                                                                                                                                                                                                    | 30 |

| Figure 27. Volume fraction of c-Si as a function of hydrogen dilution for different levels of CO <sub>2</sub> in the discharge                                                                                                                                                                                                                         | 32 |

| Figure 28. Raman spectra of ultra-thin films ( $\approx 150 \text{Å}$ ) deposited on an interlayer of $\approx \! 10 \text{Å SiO}_x$ .                                                                                                                                                                                                                 | 33 |

| Figure 29. Raman spectra of microcrystalline n-layers deposited from CO <sub>2</sub> containing discharge.                                                                                                                                                                                                                                             | 34 |

| Figure 30. Transmission of SnO <sub>2</sub> films before and after various H <sub>2</sub> treatments: (a) Asahi SnO <sub>2</sub> after H <sub>2</sub> plasma treatments at 150 or 200°C; (b) AFG SnO <sub>2</sub> after H <sub>2</sub> plasma treatments at 150 or 200°C; (c) Asahi and AFG SnO <sub>2</sub> after 400°C H <sub>2</sub> /Ar treatment. | 38 |

| Figure 31. Electronic properties of Asahi, AFG and LOF SnO <sub>2</sub> before and after H <sub>2</sub> plasma treatments at 100, 150 and 200°C, and H <sub>2</sub> /Ar treatments at 200, 300 and 400°C: (a) sheet resistance; (b) mobility; and (c) carrier density                                                                                  | 39 |

| Figure 32. Transmission of Asahi SnO <sub>2</sub> with 20 nm ZnO layer following H <sub>2</sub> plasma or H <sub>2</sub> /Ar treatments as shown                                                                                                                                                                                                       | 40 |

| Figure 33. Electronic properties of Asahi SnO <sub>2</sub> with 20 or 60 nm ZnO layers before and after H <sub>2</sub> plasma treatments at 100, 150, and 200°C (open symbols), and H <sub>2</sub> /Ar treatments at 200, 200, and 400°C (closed symbols): (a) sheet resistance; and (b) mobility.                                                     | 41 |

| Figure 34. Enhancement <i>m</i> for devices with all 4 combinations of SnO <sub>2</sub> with d = 0.14 μm.                                                                                                                                                                                                                                              | 49 |

| Figure 35. Absorption (A = 1-T-R) in glass/HTX/a-Si/BR, glass/LTX/a-Si (solid line) or glass/a-Si (open circles) structures. The a-Si was 0.5 μm. Devices without BR contact listed as having "air" as BR                                                                                                                                              | 50 |

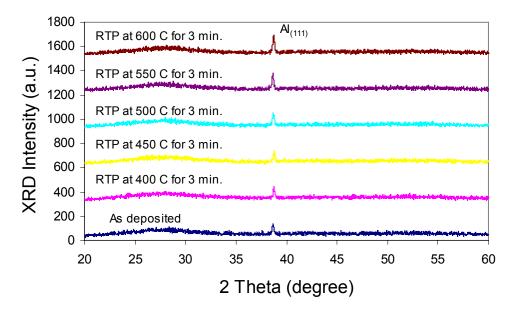

| Figure 36. XRD patterns of HW159-22 before and after RTP                                                                                                                                                                                                                                                                                               |    |

| Figure 37. XRD patterns of HW159-32 before and after RTP                                                                                                                                                                                                                                                                                               |    |

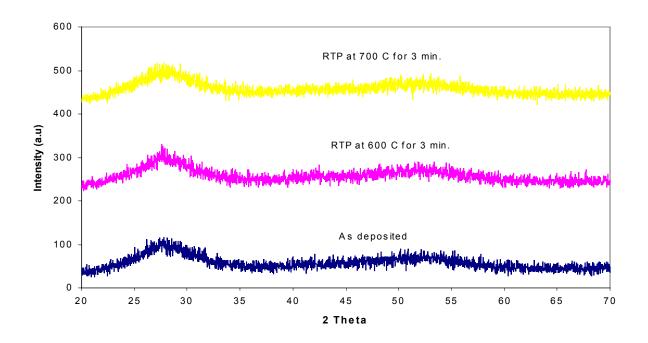

| Figure 38. XRD patterns of HW92-13 before and after RTP                                                                                                                                                                                                                                                                                                |    |

| Figure 39. XRD patterns of HW115-33 before and after RTP                                                                                                                                                                                                                                                                                               |    |

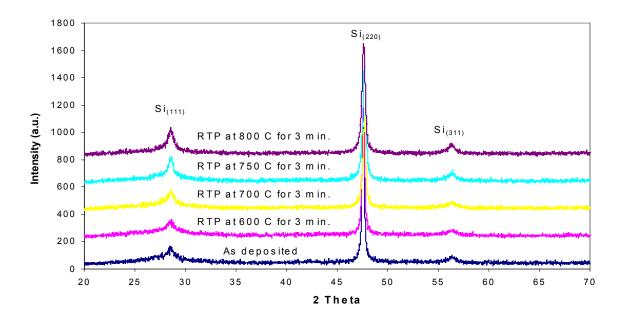

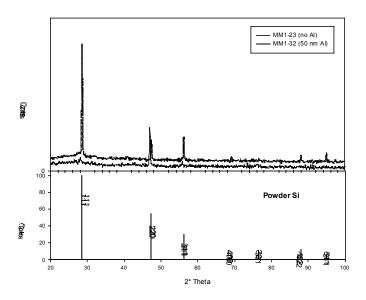

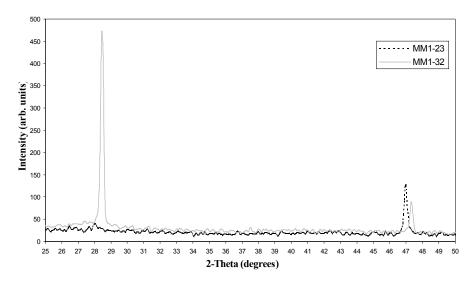

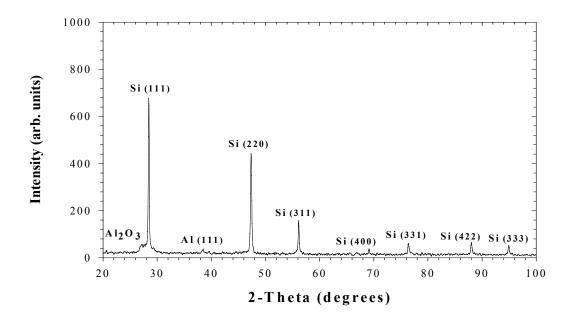

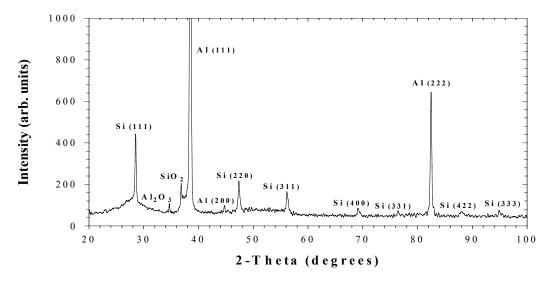

| Figure 40. XRD pattern of Si film grown on glass (no Al), on glass/50 nm Al (top), and powder Si (bottom)                                                                                                                                                                                                              | 55 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 41. XRD pattern of selected samples in detail, (111) and (220) peaks                                                                                                                                                                                                                                            | 56 |

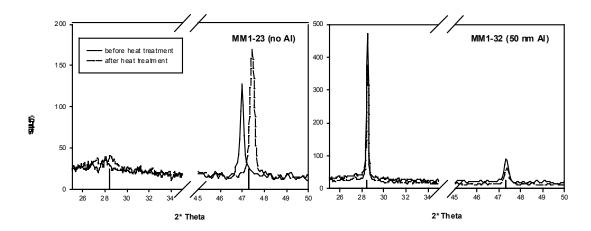

| Figure 42. Effect of heat treatment on samples                                                                                                                                                                                                                                                                         | 57 |

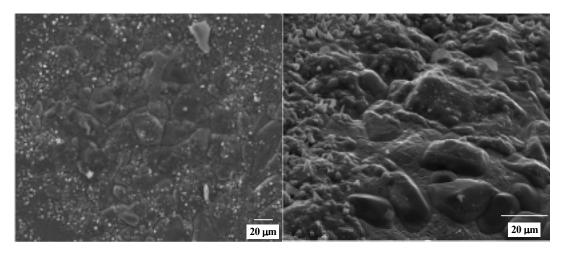

| Figure 43. XRD pattern of Si film MM3-11.                                                                                                                                                                                                                                                                              | 58 |

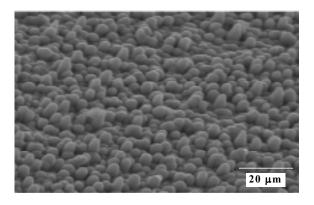

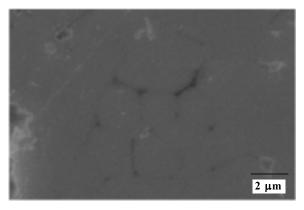

| Figure 44. SEM images of Si film MM3-11.                                                                                                                                                                                                                                                                               | 59 |

| Figure 45. XRD pattern of Si film MM4-22.                                                                                                                                                                                                                                                                              | 60 |

| Figure 46. SEM image of as-deposited Si film MM4-22.                                                                                                                                                                                                                                                                   | 60 |

| Figure 47. SEM image of polished Si film MM4-22                                                                                                                                                                                                                                                                        | 60 |

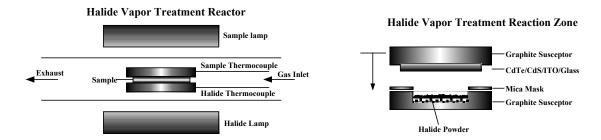

| Figure 48. Schematic views of halide vapor treatment reactor.                                                                                                                                                                                                                                                          | 64 |

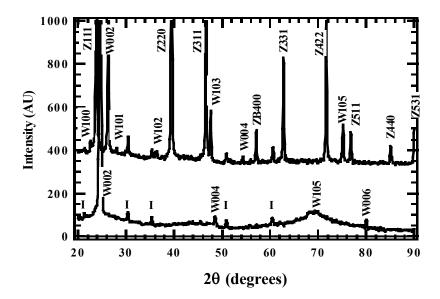

| Figure 49. XRD patterns for CdTe <sub>0.4</sub> S <sub>0.4</sub> as deposited (lower) and after treatment at 415°C in CdCl <sub>2</sub> :Ar:O <sub>2</sub> for 60 minutes. ITO substrate is indicated by "I". Zincblende and wurtzite phases and corresponding (hkl) are indicated by "Zhkl" and "Whkl", respectively. | 68 |

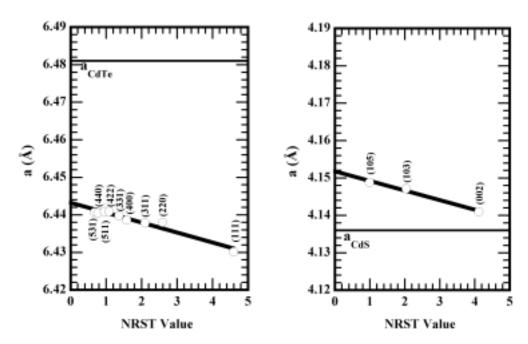

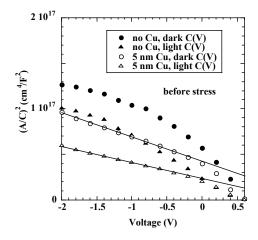

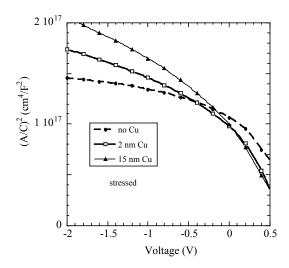

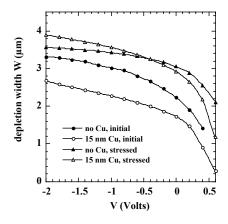

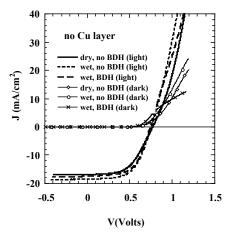

| Figure 50. Lattice parameter versus NRST function value for zincblende and wurtzite phases of film shown in Figure 49 for CdTe <sub>0.6</sub> S <sub>0.4</sub> after treatment. Horizontal lines indicate the lattice parameter values for pure CdTe and CdS.                                                          | 68 |