# Investigation of Sub-Bandgap Emission and Unexpected n-Type Behavior in Undoped Polycrystalline CdSe<sub>x</sub>Te<sub>1-x</sub>

Deborah L. McGott, Steven W. Johnston, Chun-Sheng Jiang, Tuo Liu, Darius Kuciauskas, Stephen Glynn, and Matthew O. Reese\*

Se alloying has enabled significantly higher carrier lifetimes and photocurrents in CdTe solar cells, but these benefits can be highly dependent on  $CdSe_xTe_{1-x}$  processing. This work evaluates the optoelectronic, chemical, and electronic properties of thick (3 µm) undoped  $CdSe_xTe_{1-x}$  of uniform composition and varied processing conditions ( $CdSe_xTe_{1-x}$  evaporation rate,  $CdCl_2$  anneal, Se content) chosen to reflect various standard device processing conditions. Sub-bandgap defect emission is observed, which increased as Se content increased and with "GrV-optimized  $CdCl_2$ " (i.e.,  $CdCl_2$  anneal conditions used for group-V-doped devices). Low carrier lifetime is found for GrV-optimized  $CdCl_2$ , slow  $CdSe_xTe_{1-x}$  deposition, and low-Se films. Interestingly, all films (including CdTe control) exhibited n-type behavior, where electron density increased with Se up to an estimated  $\approx 10^{17}$  cm<sup>-3</sup>. This behavior appears to originate during the  $CdCl_2$  anneal, possibly from Se diffusion leading to anion vacancy (e.g.,  $V_{Se}$ ,  $V_{Te}$ ) and  $Cl_{Te}$  generation.

# 1. Introduction

Cadmium telluride (CdTe) photovoltaics (PV) are important to the health of the U.S. PV market, making up  $\sim\!40\%$  of the utility-scale market and  $\approx\!25\%$  of plants >1 MW.  $^{[1,2]}$  Since 2002, device efficiency has improved from 16.7 to 22.6%,  $^{[3,4]}$  where increases up to 22.1% were largely enabled by Se alloying at the front of the absorber to form CdSe  $_{\rm x}$  Te  $_{\rm 1-x}$  (CST).  $^{[5]}$  This allowed for bandgap engineering and led to significant boosts in current density, carrier lifetime, and deep-level defect passivation.  $^{[6-10]}$  The final 0.5% improvement resulted from a shift in doping chemistry from Cu, which has largely limited absorber hole density to mid  $10^{14}$  cm $^{-3}$ , to group V dopants ("GrV", e.g., As, P), which has enabled carrier concentrations >10  $^{16}$  cm $^{-3}$  in polycrystalline

D. L. McGott, S. W. Johnston, C.-S. Jiang, T. Liu, D. Kuciauskas, S. Glynn, M. O. Reese

National Renewable Energy Laboratory Golden, CO 80401, USA

E-mail: Matthew.Reese@nrel.gov

The ORCID identification number(s) for the author(s) of this article can be found under https://doi.org/10.1002/advs.202309264

© 2024 The Author(s). Advanced Science published by Wiley-VCH GmbH. This is an open access article under the terms of the Creative Commons Attribution License, which permits use, distribution and reproduction in any medium, provided the original work is properly cited.

DOI: 10.1002/advs.202309264

devices.<sup>[11-13]</sup> As absorber hole density increases, theoretical studies have shown recombination at or near the front interface becomes limiting.<sup>[14-16]</sup> Thus, it is increasingly important to not only understand the improvements enabled by Se alloying, but also what losses might originate in the CdSe<sub>v</sub>Te<sub>1,v</sub> layer.

This work attempts to isolate Se-related losses by studying thick (3 μm) evaporated CdSe<sub>0.3</sub>Te<sub>0.7</sub>, the composition used in champion NREL devices, with no intentional doping and processing conditions varied to reflect standard device processing. Conditions evaluated were CdSe<sub>0.3</sub>Te<sub>0.7</sub> deposition rate (reflective of historically-used slow growth versus recent faster growth), CdCl<sub>2</sub> anneal conditions (i.e., optimized for Cu- vs GrV-doped devices), and CdSe<sub>x</sub>Te<sub>1.x</sub> composition (reflective of

different source materials tested before arriving at CdSe<sub>0.3</sub>Te<sub>0.7</sub> as the "baseline"). Optoelectronic, chemical, and electrical properties of test structures were characterized using a suite of techniques including photoluminescence (PL), time-resolved photoluminescence (TRPL), Auger electron spectroscopy (AES), deeplevel transient spectroscopy (DLTS), and scanning-spreading resistance microscopy (SSRM). Sub-bandgap defect emission ≈100-200 meV from the exciton peak was observed, which increased relative to the exciton peak as Se content increased and with "GrV-optimized CdCl<sub>2</sub>" (i.e., CdCl<sub>2</sub> anneal conditions used for GrV-doped devices). Lifetime decreased with decreasing Se content; for CdSe<sub>0.3</sub>Te<sub>0.7</sub>, both a slow deposition rate and GrVoptimized CdCl<sub>2</sub> dramatically decreased lifetime (from 920 ns to 140–150 ns). The low lifetime in "slow deposition CdSe<sub>0.3</sub>Te<sub>0.7</sub>" is attributed to reduced Se content in the final film (measured  $CdSe_{0.23}Te_{0.77}$  via AES) with additional losses potentially from anion vacancy (i.e.,  $\rm V_{Se}$  ,  $\rm V_{Te})$  generation. Low lifetime in  $\rm CdSe_{0.3}Te_{0.7}$ with GrV-optimized CdCl2 appeared to result from increased nonradiative recombination, possibly from a broader band of defects relative to CdSe<sub>0.3</sub>Te<sub>0.7</sub> with Cu-optimized CdCl<sub>2</sub> ("base-

"Undoped" CdTe and CdSe $_{\rm x}$ Te $_{\rm 1.x}$  are typically thought to be slightly p-type, usually due to Cd vacancies and/or Cu dopants unintentionally introduced during the CdCl $_{\rm 2}$  anneal. [17,18] All films studied here, however, were found to be n-type where electron density increased with Se content from barely detectable (CdTe) to  $\approx 10^{16}-10^{17}$  cm $^{-3}$  for CdSe $_{0.3}$ Te $_{0.7}$  and CdSe $_{0.4}$ Te $_{0.6}$ , despite using conditions similar to standard device processing.

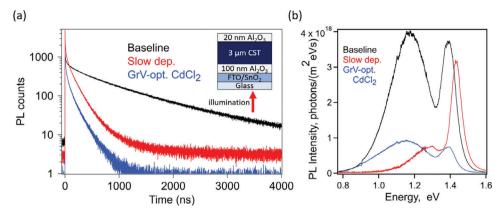

**Figure 1.** a) TRPL and b) spectrally corrected absolute PL for double heterostructures (stack shown in the inset of panel a) evaporated from an alloyed  $CdSe_{0.3}Te_{0.7}$  source with "baseline" conditions (16 Å s<sup>-1</sup> CST deposition,  $CdCl_2$  anneal developed for Cu-doped devices – black traces), "slow dep." (2 Å s<sup>-1</sup> CST deposition – red traces), and "GrV-opt.  $CdCl_2$ " ( $CdCl_2$  anneal conditions optimized for GrV-doped devices – blue traces).

The strong n-type behavior in the absence of intentional doping is surprising, particularly since electron density is about the same as the desired hole density in GrV-doped devices. Throughout the work, we develop the hypothesis that this n-type behavior, and possibly sub-bandgap defect emission, originate from the  $\mathrm{CdCl}_2$  anneal. Specifically, anion vacancies may form more readily in  $\mathrm{CdSe}_x\mathrm{Te}_{1-x}$  than  $\mathrm{CdTe}_x^{[17]}$  which could then be filled with chlorine to form  $\mathrm{Cl}_{\mathrm{Te}}$ , a known shallow donor defect in  $\mathrm{CdTe}_x^{[19-21]}$  Unintentional n-type behavior in  $\mathrm{CdSe}_x\mathrm{Te}_{1-x}$  at the front of devices could result in losses from buried junction effects, compensation, low activation, and so on.

For clarity, characterization results are first presented with minimal analysis in Section 2. After all results are presented, they are analyzed and discussed en masse in Section 3, which is divided into three subsections to highlight and evaluate the significance of the results in their varied aspects. Section 3.1 explores the effect that processing conditions have on performance; Section 3.2 discusses the observed n-type behavior and its implications in devices; and Section 3.3 takes a deeper dive into possible underlying mechanisms.

### 2. Results

Figure 1 shows PL-related data for CdSe<sub>0.3</sub>Te<sub>0.7</sub> double heterostructures (DHs-3 μm thick CdSe<sub>0.3</sub>Te<sub>0.7</sub> sandwiched between two passivating Al<sub>2</sub>O<sub>3</sub> layers, film stack shown in Figure 1a inset) with (black trace) "baseline" conditions for high lifetime test structures, i.e., evaporation from a CdSe<sub>0.3</sub>Te<sub>0.7</sub> alloyed source at 16 Å s<sup>-1</sup> and CdCl<sub>2</sub> anneal conditions developed for Cu-doped devices; (red trace) "slow dep.", i.e., 2 Å s<sup>-1</sup> deposition (reflective of historically used processing) rather than 16 Å s<sup>-1</sup> and same CdCl<sub>2</sub> anneal; and (blue trace) "GrV-optimized CdCl<sub>2</sub>," 16 Å s<sup>-1</sup> deposition and CdCl<sub>2</sub> anneal developed for GrV-doped devices. "Baseline" CdCl<sub>2</sub> anneal conditions were 500 °C for 10 min under 400 Torr He. These are standard processing conditions for test structures as they have been shown to maximize carrier lifetimes, [8] but are slightly more "aggressive" than CdCl<sub>2</sub> anneals typically done in devices (450-480 °C), as devices tend to start delaminating at  $\approx$ 500 °C.

Minority carrier lifetime in the bulk<sup>[14]</sup> was calculated by fitting the "tail" of TRPL decays (at long time scales) in Figure 1a using:

$$I(t) = I_0 e^{-t/\tau_2} (1)$$

where I(t) = intensity,  $I_0$  = initial intensity, t = time, and  $\tau_2$  = minority carrier lifetime of the tail.  $\tau_2$  values are listed in **Table** 1. TRPL was collected at wavelengths between about 700 and 1100 nm (energy between ≈1.1 and 1.8 eV) using a 700 nm longpass filter and Si avalanche photodiode detector. While baseline CdSe<sub>0.3</sub>Te<sub>0.7</sub> showed a high  $\tau_2$  of 920 ns, the "slow deposition" and "GrV-optimized CdCl<sub>2</sub>" CdSe<sub>0.3</sub>Te<sub>0.7</sub> only reached 140-150 ns. The absolute PL in Figure 1b shows a large defect peak  $\approx$ 200 meV below the exciton peak for baseline CdSe<sub>0.3</sub>Te<sub>0.7</sub> (it is important to note this does not necessarily equate to the thermal activation energy of the defect). Under slow deposition conditions, the defect peak height decreased relative to the exciton peak, and with "GrV-optimized CdCl2," the overall luminescence decreased but the defect peak grew relative to the exciton peak (see Figure S1, Supporting Information for normalized PL data). Photoluminescence quantum yield (PLQY, integration under the entire PL curve) is listed in Table 1.

AES was used to measure Se/(Se+Te) ratios (also called Se %, concentration, or content in this work) in the CdCl<sub>2</sub>-treated CdSe<sub>x</sub>Te<sub>1-x</sub> films by cleaving at the Al<sub>2</sub>O<sub>3</sub>/CdSe<sub>x</sub>Te<sub>1-x</sub> interface and ion milling (see Experimental Section for details); values are given in Table 1. While "GrV-optimized CdCl<sub>2</sub>" conditions did not significantly impact Se concentration, reducing the CdSe<sub>0.3</sub>Te<sub>0.7</sub> deposition rate from 16 to 2 Å s<sup>-1</sup> caused Se in the film to drop from 29 to 23 at%. This is discussed further in Section 3.1.

SSRM is an atomic force microscopy (AFM)-based electrical technique used for nm-scale resistance mapping (typically with a spatial resolution of 10–50 nm, depending on sample and probe conditions). While the resistance along the entire current path through the film stack is involved, the SSRM-measured resistance ( $R_{\rm tot}$ ) is dominated by spreading resistance beneath the probe ( $R_{\rm sp}$ , see Experimental Section for discussion), where the probe depth is  $\approx 50$  nm. The change in  $R_{\rm tot}$  as bias voltage is switched from positive to negative polarity can give insight into carrier type. SSRM was measured on CdCl<sub>2</sub>-treated cleaved CdSe<sub>0.3</sub>Te<sub>0.7</sub> with Au back contacts;  $R_{\rm tot}$  is listed in Table 1. In-

and-conditions) on Wiley Online Library for rules of use; OA articles are governed by the applicable Creative Commons

ADVANCED SCIENCE

Table 1. Measured parameters for CdSe<sub>x</sub>Te<sub>1-x</sub> evaporated from an alloyed CdSe<sub>0.3</sub>Te<sub>0.7</sub> source with "baseline" conditions (16 Å s<sup>-1</sup> deposition, CdCl<sub>2</sub> anneal developed for Cu-doped devices), "slow deposition" (2 Å s<sup>-1</sup> deposition rather than 16 Å s<sup>-1</sup>), or "GrV-optimized CdCl<sub>2</sub>" conditions (CdCl<sub>2</sub> anneal developed for GrV-doped devices). Carrier lifetime ( $\tau_2$ ) measured via TRPL; energy at exciton and defect peak maxima ( $E_{exciton}$  and  $E_{defect}$ , respectively) and photoluminescence quantum yield (PLQY) obtained from PL; Se/(Se+Te) in the final CdCl<sub>2</sub>- treated film measured via AES; average resistance measured using SSRM under –5 V sample bias voltage ( $R_{tot}$ ); and grain size measured with bright-field optical microscope.

|                                 | τ <sub>2</sub> [ns] | E <sub>exciton</sub> [eV] | E <sub>defect</sub> [eV] | PLQY    | Se/(Se+Te) | $R_{tot} [\Omega]$ | Avg. grain size [μm] |

|---------------------------------|---------------------|---------------------------|--------------------------|---------|------------|--------------------|----------------------|

| Baseline                        | 920                 | 1.39                      | 1.17                     | 7.2E-04 | 29         | 5.5E + 04          | 1.9 ± 0.1            |

| Slow deposition                 | 150                 | 1.43                      | 1.30                     | 2.2E-04 | 23         | 3.7E + 05          | $2.2 \pm 0.3$        |

| GrV-optimized CdCl <sub>2</sub> | 140                 | 1.39                      | 1.16                     | 1.9E-04 | 27         | 4.4E + 04          | $2.1 \pm 0.1$        |

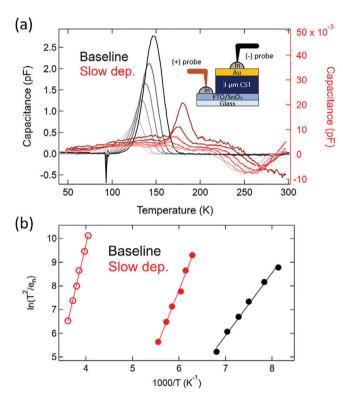

**Figure 2.** DLTS measurements showing a) capacitance as a function of temperature for varied transient time windows (from lightest to darkest = 100, 50, 20, 10, 5, and 2 ms) and b) Arrhenius plot using the peak temperature values for the corresponding time windows where closed circles represent minority carrier (hole) traps and open circles represent majority carrier (electron) traps. Black tones represent baseline  $CdSe_{0.3}Te_{0.7}$  and red tones represent "slow deposition  $CdSe_{0.3}Te_{0.7}$ " (measured  $CdSe_{0.23}Te_{0.77}$ ). Inset of (a) shows the device stack measured and reversed polarity of probes required for measurement.

terestingly, all films showed n-type behavior (Figure S2, Supporting Information), which was corroborated by the Hall effect (not shown, done on cleaved  $CdSe_xTe_{1-x}$  films with no back contact) and the probe polarity required to measure DLTS (reversed from a standard p-type structure, shown in **Figure 2a** inset). It was surprising that these films were measurable via Hall since polycrystalline CdTe-based materials (no intentional doping) are typically below the detection limit of the system used ( $\approx 10^{16}$  cm<sup>-3</sup>).

A rough estimate for electron density can be extracted from  $R_{\text{tot}}$  using:

$$\frac{1}{\rho} = qC\mu = \frac{1}{4rR} \tag{2}$$

where  $\rho$  = resistivity, q = elemental charge, C = charge concentration,  $\mu$  = mobility, r = probe/sample contact radius, and R = measured resistance. Calculated electron density for CdSe<sub>0.3</sub>Te<sub>0.7</sub> with baseline conditions and "GrV-optimized CdCl<sub>2</sub>" was  $\approx 10^{17}$  cm<sup>-3</sup> and electron density for "slow deposition CdSe<sub>0.3</sub>Te<sub>0.7</sub>" (actually CdSe<sub>0.23</sub>Te<sub>0.77</sub>) was  $\approx 10^{16}$  cm<sup>-3</sup>, assuming electron mobility in all films is relatively constant. However, it is unclear if this is a fair assumption as mobility may change significantly with Se alloying, [23] so electron densities are not given in Table 1.  $R_{\rm tot}$  was uniform laterally, across grain boundaries (GBs; example in Figure S2b, Supporting Information), and throughout the thickness (Figure S2g, Supporting Information).  $R_{\rm tot}$  was measured across 12 µm; grain size for all three films was  $\approx 2$  µm (see Figure S3, Supporting Information); Table 1).

DLTS is used to measure the transient capacitance change after deep-level traps in the space charge region are filled with either majority- or minority-carrier charges. Figure 2 shows DLTS results for baseline CdSe<sub>0.3</sub>Te<sub>0.7</sub> and "slow deposition CdSe<sub>0.3</sub>Te<sub>0.7</sub>" (both CdCl2-treated) with SnO2:F/SnO2 as the front contact and Au as the back contact. CdSe<sub>0.3</sub>Te<sub>0.7</sub> with GrV-optimized CdCl<sub>2</sub> was not measurable via DLTS or capacitance-voltage (CV, not shown) and behaved as if contact was not being made. This may indicate an issue with one or both contacts and is discussed in Section 3.1. As mentioned above, probe polarity during DLTS measurement was reversed from what would typically be used for p-type absorbers (Figure 2a inset). This suggests that the back Schottky barrier was probed rather than the front (typically p-n but in this case n-n) heterojunction. Because of this, and due to buried junction effects observed previously in graded CST devices<sup>[24]</sup> which would dominate the capacitance signal at the front, it is not likely that effects such as band offset at the SnO<sub>2</sub>/CST interface have a significant impact on DLTS measurements.

The positive peaks in Figure 2a indicate minority carrier trapping, which in n-type material are hole traps. Baseline  $CdSe_{0.3}Te_{0.7}$  has a hole trap while "slow deposition  $CdSe_{0.3}Te_{0.7}$ " (measured  $CdSe_{0.23}Te_{0.77}$ ) shows a hole trap and a negative peak corresponding to a majority carrier (electron) trap that forms at higher temperature, giving a defect level deeper in the bandgap. For both samples, peak heights, and widths increased as the transient time window decreased, suggesting nonexponential decay shapes and a band of defects rather than a low concentration of point defects. Figure 2b shows an Arrhenius plot for the two samples from which activation energy ( $E_A$ ) of the carrier traps, carrier density ( $N_S$ ), and trap density ( $N_T$ ) are extracted; values are listed in Table 2. Changes in peak height were still observed at the lowest time resolution of the DLTS system, so the calculated

www.advancedscience.com

**Table 2.** Measured DLTS parameters for  $CdSe_xTe_{1.x}$  evaporated from an alloyed  $CdSe_{0.3}Te_{0.7}$  source with "baseline" and "slow deposition" conditions  $(CdSe_{0.3}Te_{0.7}$  with "GrV-optimized  $CdCl_2$ " could not be measured). Activation energy  $(E_A)$ , carrier density  $(N_S)$ , trap density  $(N_T)$ , and apparent capture cross section  $(\sigma_a)$  were calculated from the DLTS data. The "slow dep. (electron trap)"  $E_A$  is with respect to the conduction band and  $N_S$  = holes; "baseline" and "slow dep. (hole trap)"  $E_A$  is with respect to the valence band and  $N_S$  = electrons.

|                           | E <sub>A</sub> [eV] | $N_S$ [cm $^{-3}$ ] | $N_T$ [cm <sup>-3</sup> ] | $\sigma_{\rm a}~{\rm [cm^2]}$ |

|---------------------------|---------------------|---------------------|---------------------------|-------------------------------|

| Baseline                  | 0.23 ± 0.01         | 7.9E + 15           | 4.8E + 14                 | 7.6E-17                       |

| Slow dep. (hole trap)     | $0.42 \pm 0.02$     | 1.6E + 14           | 4.8E + 12                 | 4.0E-13                       |

| Slow dep. (electron trap) | $0.70 \pm 0.02$     | 1.6E + 14           | 1.8E + 12                 | 1.3E-12                       |

**Table 3.** Measured parameters for CdSe<sub>x</sub>Te<sub>1-x</sub> evaporated from alloyed source powders with x = 0, 0.1, 0.2, 0.3 (copied from above), and 0.4 under baseline conditions (16 Å s deposition, CdCl<sub>2</sub> developed for Cu-doped devices).  $\tau_2$  was measured via TRPL;  $E_{exciton}$ ,  $E_{defect}$ , and PLQY via PL; Se/(Se+Te) measured in the final films via AES;  $R_{tot}$  measured using SSRM; and grain size measured with bright-field optical microscope.

|                      | τ <sub>2</sub> [ns] | E <sub>exciton</sub> [eV] | E <sub>defect</sub> [eV] | PLQY    | Se/(Se+Te) | R <sub>tot</sub> [Ω] | Avg. grain size [μm] |

|----------------------|---------------------|---------------------------|--------------------------|---------|------------|----------------------|----------------------|

| CdTe                 | 33                  | 1.50                      | N/A                      | 9.9E-06 | 0          | 1.7E+06              | 3.2 ± 0.3            |

| $CdSe_{0.1}Te_{0.9}$ | 42                  | 1.46                      | N/A                      | 1.7E-05 | 8          | 9.0E+05              | $3.4 \pm 0.1$        |

| $CdSe_{0.2}Te_{0.8}$ | 230                 | 1.43                      | 1.28                     | 6.2E-05 | 19         | 1.8E+05              | $2.3 \pm 0.2$        |

| $CdSe_{0.3}Te_{0.7}$ | 920                 | 1.39                      | 1.17                     | 7.2E-04 | 29         | 5.5E+04              | $1.9 \pm 0.1$        |

| $CdSe_{0.4}Te_{0.6}$ | 1300                | 1.38                      | 1.10                     | 5.2E-04 | 36         | 2.6E+04              | $1.6 \pm 0.2$        |

$N_{\rm T}$  is considered a lower bound. It is noted that DLTS showed similarly high electron densities to SSRM. The apparent capture cross-section ( $\sigma_{\rm a}$ ) of the hole traps is calculated assuming a hole-effective mass of 0.63  $\rm m_{\rm o}$  (where  $\rm m_{\rm o}$  is electron mass). [26] It is noted, however, that this value may hold little physical relevance if there is any temperature dependence in the capture rate.

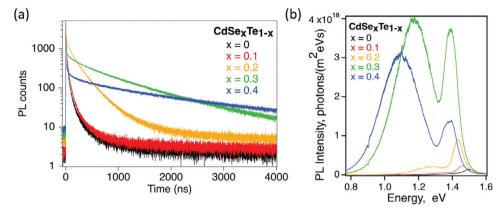

Using baseline conditions (16 Å s<sup>-1</sup> deposition, CdCl<sub>2</sub> developed for Cu-doped devices), Se % was varied by evaporating from alloyed CdSe<sub>x</sub>Te<sub>1-x</sub> sources with x = 0 (CdTe), 0.1, 0.2, and 0.4, in addition to the x = 0.3 explored above. This series was done in a more complete sweep since CdSe<sub>x</sub>Te<sub>1-x</sub> composition is graded in devices. **Table 3** lists extracted characterization data similar to Table 1. **Figure 3** shows TRPL and absolute PL data; normalized PL data is in Figure S4 (Supporting Information). Generally, the measured Se % in the films was close to but slightly below the source material, suggesting a slight loss of Se during deposition and/or during subsequent CdCl<sub>2</sub> treatment. Se concentration and  $E_{\text{exciton}}$  (often equated with bandgap) measured here agree with literature demonstrating a bandgap "bowing" effect in CdSe<sub>x</sub>Te<sub>1-x</sub>.<sup>[27]</sup>

As Se increased,  $\tau_2$  increased (in agreement with previous studies),[7,8] defect emission increased (in agreement with previous studies),[23,28,29] grain size decreased (Figure S5, Supporting Information, also in agreement with previous studies), [30] and R<sub>tot</sub> decreased (i.e., electron density increased). All films, including CdTe, demonstrated n-type behavior despite using processing conditions standardly used for high-lifetime test structures<sup>[8,31,32]</sup> and expected to result in slightly p-type films. The measured resistance decreased by two orders of magnitude when Se content increased from 0% (CdTe) to ≈40%, indicating electron density likely increases by a similar amount assuming mobility stays relatively unchanged. It is noted, however, that CdTe, CdSe<sub>0.1</sub>Te<sub>0.9</sub>, and CdSe<sub>0.2</sub>Te<sub>0.8</sub> were too resistive to be measured via Hall (with measurement threshold  ${\approx}10^{16}~\text{cm}^{-3}\text{)}$  and CV showed decreasing capacitance with voltage for both probe polarities on CdTe, so it is likely only lightly n-type.

### 3. Discussion

The above results are now discussed in an integrated manner where discussion is divided into three sections. The first section focuses on the effect processing conditions have on  $CdSe_xTe_{1-x}$  performance, particularly carrier lifetime. The second section discusses the n-type behavior observed here and its potential implications in devices. The third section explores mechanisms, including Se- and Cl-related defects, which may be responsible.

# 3.1. Processing Parameters Effect on Performance

One of the major benefits of alloying CdTe with Se is the significantly improved carrier lifetime. However, lifetime was shown to be strongly dependent on processing conditions, which can vary widely between institutions. In particular, deposition rate, which is often not even listed in experimental sections, showed a dramatic effect on carrier lifetime when the CdSe<sub>0.3</sub>Te<sub>0.7</sub> source was evaporated slowly (i.e., sample and source held at high temperature under vacuum for longer). Importantly, AES showed slow deposition resulted in reduced Se % in the final film (CdSe<sub>0.23</sub>Te<sub>0.77</sub> measured), possibly resulting in a high density of anion vacancies which can act as nonradiative recombination centers, reducing lifetime and luminescence. While the CdTe community has largely not considered preferential loss of Se during high-temperature deposition of Se-containing films, it is not unknown. In fact, binary CdSe films are commonly n-type from high densities of  $V_{Se}$ , [33,34] and evaporation of CuIn, Ga1.x Se2 is frequently done with a Se overpressure to prevent V<sub>Se</sub> formation.<sup>[35]</sup>

Here, it appears changes in TRPL and PL can mostly be explained by the lower Se content, as the  $CdSe_{0.23}Te_{0.77}$  (slow deposition) sample closely resembled  $CdSe_{0.19}Te_{0.81}$  (deposited from a  $CdSe_{0.2}Te_{0.8}$  source) with regard to grain size,  $R_{tot}$ ,  $\tau_2$ , and, remarkably, PL curves looked nearly identical when normalized (see Figure S6 and Table S1, Supporting Information for di-

and-conditions) on Wiley Online Library for rules of use; OA articles are governed by the applicable Creative Commons

Figure 3. a) TRPL and b) absolute spectrally corrected PL showing the effect of increasing Se concentration in  $CdSe_xTe_{1-x}$  from x = 0 to 0.4 (referring to the alloyed source material composition) with baseline conditions; x = 0.3 data copied here for reference.

rect comparison between the two). Additional losses in lifetime (i.e., the  $CdSe_{0.23}Te_{0.77}$  slow deposition sample was 150 ns while  $CdSe_{0.19}Te_{0.81}$  was 230 ns) may be due to anion vacancies and/or other defect chemistries, as discussed in Section 3.3. This may be reflected in the difference in DLTS between baseline and slow deposition  $CdSe_{0.3}Te_{0.7}$  seen in Figure 2. It could be that as the density of defects that dominates the sub-bandgap PL peak and capacitance for baseline  $CdSe_{0.3}Te_{0.7}$  decrease, a defect(s) deeper in the band becomes visible, or it could be the same defect shifted deeper under "slow deposition" conditions. Further research is required.

An important recent shift in processing for the CdTe community has been from Cu to GrV doping, for which CdCl<sub>2</sub> anneal conditions have been re-optimized. Here, CdSe<sub>0.3</sub>Te<sub>0.7</sub> treated with GrV-optimized CdCl<sub>2</sub> conditions showed substantially lower lifetime than baseline (i.e., Cu-optimized CdCl<sub>2</sub>) CdSe<sub>0.3</sub>Te<sub>0.7</sub> (140 and 920 ns, respectively). Together with decreased PLQY and broadened defect peak, low lifetime likely results from increased nonradiative recombination and a broader band of defects. Since CST is typically responsible for high lifetimes in Cu-doped devices, this reduced lifetime with GrV-optimized CdCl2 may be a reason that GrV-doped devices can suffer from relatively low lifetimes, particularly when absorber hole density is low.[18] Unfortunately, DLTS (or CV) could not be measured on these samples; SSRM, however, was measurable. Because DLTS and CV require current flow through both contacts while SSRM only requires an intact back contact (see Experimental Section), this suggests that the SnO<sub>2</sub>/CdSe<sub>0.3</sub>Te<sub>0.7</sub> interface may be damaged during the "GrV-optimized CdCl2" anneal (i.e., defect density greatly increased - GrV-dopant pileup is regularly observed in devices and may be related).[3,36] In highly doped GrV devices, this issue may be exacerbated by the increased sensitivity to front interface recombination.[14-16]

Finally, the samples with the highest PLQY, which is typically taken as an indication of better material passivation, [7.8,37,38] also showed the highest sub-bandgap emission (e.g.,  $CdSe_{0.3}Te_{0.7}$  and  $CdSe_{0.4}Te_{0.6}$  in Figure 3b). This raises the question of whether high PLQY (integration under the entire PL curve) always indicates good material quality. Since increasing defect emission with higher Se content has been observed for undoped CST fabricated at other institutions using different methods, [28,39] this hints at a

fundamental defect that may lead to losses in devices. It is unclear how harmful these defects are though, since Cu-doped devices with CdSe<sub>0.3</sub>Te<sub>0.7</sub> at the front still achieve high carrier lifetime and photocurrent.<sup>[31,40]</sup> Because the defects are radiative and relatively shallow, it is possible that the long carrier lifetimes originate from the trapping/de-trapping of minority carriers (holes).<sup>[23]</sup> This is supported by DLTS, which showed the dominance of hole trapping in these films. TRPL curves do not suggest detrimental trapping though (i.e., nearly complete decay within first few nanoseconds followed by a flat tail hovering just above baseline),<sup>[41]</sup> likely because deep (nonradiative) defects in CdTe are passivated by Se.<sup>[6,10]</sup> Passivation of deep defects and introduction of shallow hole traps at GBs via Se and Cl<sup>[10]</sup> may be a reason that lifetime and conductivity increased as grain size decreased (Figure S7, Supporting Information), both unexpected trends.

Because SSRM did not show a distinguishable difference between GBs and grain interiors (GIs), this suggests that electron density is within a factor of ten between the two. Since the GB region is likely only a few atomic layers thick (less than a few nanometers), it is possible that the resistivity change around the GB is not detected via SSRM, which has a spatial resolution of 10–50 nm. It is noted, however, that changes in GB resistivity have been detected for CdTe and other PV materials using the same SSRM tool previously.<sup>[42,43]</sup> Additionally, a large forward bias (5 V) is applied during SSRM measurement to overcome probe/sample contact resistance (see Experimental Section) so any band bending around GBs, e.g., as has been shown in graded devices previously, <sup>[10,44]</sup> becomes flattened and only intrinsic GI and GB resistivity are measured.

### 3.2. N-Type Behavior

This section explores potential causes for the observed strong n-type behavior and implications for device performance. Binary CdSe films are commonly n-type,  $^{[33,34]}$  so it was questioned whether n-type behavior could originate from phase segregation into Se-rich and Se-poor regions, which would have wurtzite and zincblende structures, respectively. While the literature suggests this transition may happen at compositions as low as CdSe $_{0.3}$ Te $_{0.7}$  in some cases,  $^{[45,46]}$  X-ray diffraction (XRD) analysis of the most

www.advancedscience.com

Se-rich films, CdSe<sub>0.4</sub>Te<sub>0.6</sub>, did not show evidence of the wurtzite phase here (Figure S8, Supporting Information). Some spatial variation in composition was observed in these films (Figure S9, Supporting Information), but it did not appear to affect the intrinsic electronic properties (Figure S2b, Supporting Information). Importantly, this shows that spatial nonuniformities in electrical properties seen in graded devices<sup>[46,47]</sup> are not inherent to polycrystalline CST thin films (here without intentional doping), but are likely driven by differences in composition within the stack (i.e., from sequential evaporation of CdSe or CST and CdTe followed by CdCl<sub>2</sub> treatment, or co-evaporation of CdSe and CdTe).

Several studies have shown n-type GBs in CdTe<sup>[44,48,49]</sup> and CST.<sup>[10,50,51]</sup> It is possible that a common defect chemistry is shared between GBs and GIs, and as the density of GBs increases, the density of hole traps responsible for the trends seen in this work also increases. This may be why resistance (electron density) and grain size are particularly well correlated (Figure S7, Supporting Information). Thus, GBs contribute to, but are not solely responsible for, n-type behavior in these films. By beveling the samples and measuring SSRM as a function of depth (Figure S3g, Supporting Information), it was shown that n-type behavior was uniform throughout the film and not a result of altered chemistry at the front interface (e.g., oxidation, <sup>[52,53]</sup> accumulation of Cl/CdCl<sub>2</sub>).<sup>[54]</sup> Hall effect measurements (not shown), which probe the bulk, also showed n-type behavior.

Because most studies show slightly p-type behavior in the bulk under standard device processing, particularly in CdTe, it is important to understand the conditions at which CST becomes strongly n-type, and whether it commonly is in devices. This is particularly important since the conditions used here were similar to standard device processing and are standard conditions used for test structures. Jiang et al. previously showed n-type behavior in the Se-rich region of graded CST devices (not fabricated at NREL), [24] which led to buried junction effects and associated losses. In a theoretical study by Good et al., a thin compensating layer at the front of GrV-doped devices was shown to result in dramatic  $V_{OC}$  loss. [36] Generally, donor defects are undesirable since they can compensate p-type dopants and/or compete for dopant sites (e.g., Cl or O competing with As for  $V_{Te}$  sites); see Section 3.3 for further discussion on potential defect chemistries.

High electron density (on the order of 10<sup>16</sup> cm<sup>-3</sup>) in CST may also be a reason it is more difficult to dope p-type than CdTe. [55] This could also be a reason CST-only devices (including graded CdSe<sub>0.4</sub>Te<sub>0.6</sub>/CdSe<sub>0.2</sub>Te<sub>0.8</sub> devices) do not typically perform as well as graded CST/CdTe devices. [56] In addition to the electron reflector role Shah et al. demonstrated CdTe plays at the back, [56] recombination may be lower at the back of CST/CdTe devices due to, at least partially, the reduced electron density there. Knowing that CST (no intentional doping) can be strongly n-type and accounting for this may open avenues to make highly doped ntype devices, particularly since the CST measured here showed an electron density of  $10^{16}$ – $10^{17}$  cm<sup>-3</sup> (assuming an electron mobility of 100 cm<sup>2</sup> Vs<sup>-1</sup>). Future work should evaluate whether CST in devices (which is typically treated at 450-480 °C CdCl<sub>2</sub> rather than 500°C since the latter typically causes delamination) has similarly high electron density. Finally, the inclusion of n-type CST in device models, rather than assuming it is p-type as is often done, may help elucidate differences between theoretical and measured device performance.

### 3.3. Potential n-type Defect Chemistries

This section develops arguments for which defect chemistries are likely to contribute to the trends observed in this work, namely sub-bandgap PL emission at room temperature and n-type behavior. Polycrystalline CdTe films are typically slightly Te-rich, and therefore p-type, due to the lower formation energy of cation vacancies ( $V_{\rm Cd}$ ). Additional hole density is thought to originate from Cu impurities (on Cd sites) introduced during CdCl<sub>2</sub> treatment. Is For the films studied here to be n-type (including CdTe), it is likely that a stable donor defect (or defects, defect complex(es)) has overwhelmed the intrinsic acceptor defects, potentially pinning the Fermi level and changing the conductivity. Since CdTe appeared mostly intrinsic with minimal n-type behavior, it is likely that Se plays a key role in defect generation.

Anion vacancies (V<sub>Se</sub>, V<sub>Te</sub>) are a logical assumption since binary CdSe films are typically n-type due to high densities of  $V_{Se}$ , [33,34] and  $CdSe_xTe_{1-x}$  (specifically,  $CdSe_{0.5}Te_{0.5}$ ) has been shown, theoretically, to have a lower formation energy for anion vacancies than CdTe.[17] However, anion vacancies are not thought to be solely responsible for the sub-bandgap defect emission and n-type behavior observed here for a few reasons: i) the sample expected to have the highest anion vacancy density, "slow deposition CdSe<sub>0.3</sub>Te<sub>0.7</sub>," which did have a lower measured Se % of CdSe<sub>0.23</sub>Te<sub>0.77</sub>, had higher resistance (lower electron density) and lower defect emission than baseline CdSe<sub>0.3</sub>Te<sub>0.7</sub>, ii) if CdSe, Te<sub>1,y</sub> has a higher density of isolated anion vacancies than CdTe, it would be expected to be easier to dope p-type, but the opposite is typically observed, [55] and iii) when chlorine is present, it is likely more thermodynamically favorable to form  $Cl_{Te}$  than  $V_{Te}$ in CdTe.<sup>[59]</sup> It is possible, however, that the difference in DLTS between baseline and slow deposition CdSe<sub>0.3</sub>Te<sub>0.7</sub>, namely higher activation energy and the emergence of a deep electron trap in the latter, may be related to anion vacancies; further research is required.

Since all samples required  $CdCl_2$  treatment to be measurable via PL, TRPL, DLTS, etc., it is challenging to decouple Se from Cl effects.  $Cl_{Te}$  is a known shallow donor defect in CdTe and has been identified, primarily at GBs for polycrystalline material, in both  $CdTe^{[44,48,49]}$  and  $CST,^{[10,50,51]}$  turning them n-type. Importantly, films that were not  $CdCl_2$  treated were too resistive to measure via Hall. Likewise, when the " $CdCl_2$  anneal" was done without a  $CdCl_2$  source (i.e.,  $CdSe_{0.3}Te_{0.7}$  was annealed using the same temperature profile and ambient that might generate non-Cl related defects, such as anion vacancies,  $Se_{Te}$ ,  $O_{Te}$ ), the films were too resistive to be measured. This suggests that the n-type defects that dominate here are related to chlorine and/or require the presence of  $CdCl_2$  to be generated (e.g., impurities introduced from the  $CdCl_2$  source).

Importantly, the  $CdCl_2$  anneal has been identified as the primary driver for Se diffusion in  $CST_{-}^{[60-62]}$  Because diffusion increases with temperature, it is possible that the more aggressive  $CdCl_2$  treatment used here (500 °C vs 450–480 °C commonly used in devices) moves Se around more, creating a higher probability for defect creation, whether it is impurity substitution (e.g.,  $Cl_{Te}$ ,  $O_{Te}$ ), anti-sites (e.g.,  $Se_{Te}$ ), interstitials (e.g.,  $Cd_i$ ), or vacancies (e.g.,  $V_{Se}$ ). Interstitial chlorine may also exist at high chlorine concentrations (e.g., from long and/or high-temperature  $CdCl_2$  anneals). If a high density of anion vacancies are generated dur-

www.advancedscience.com

ing the  $CdCl_2$  anneal, Cd-rich conditions would be created and the  $CdSe_xTe_{1.x}$  film may be easier to dope with Cl, as demonstrated in CdTe single crystal studies. [19,21,49]

Of course, defect complexes may also form, such as the chlorine "A-center" (V<sub>Cd</sub>-Cl<sub>Te</sub>), which acts as a shallow donor when in C<sub>S</sub> symmetry. Oxygen complexes such as the oxygen "A-center" ( $V_{\text{Cd}}$ - $O_{\text{Te}}$ ) or  $\text{Te}_{\text{Cd}}$ - $O_{\text{Te}}$  may also form, but these defects may tend to be shallow acceptors. [63,64] Divacancy complexes, e.g., V<sub>Cd</sub>-V<sub>Te</sub>, are another possibility that has been identified in CdTe films via techniques like positron annihilation spectroscopy. [65,66] If this is the case, it would parallel the defect complex thought to be responsible for recombination and metastability in CuIn<sub>x</sub>Ga<sub>1-x</sub>Se<sub>2</sub>: V<sub>Se</sub>-V<sub>Cu</sub>.<sup>[67]</sup> Further research is required to evaluate activation energy (e.g., as a function of Se content, CdCl<sub>2</sub> anneal temperature, CdSe<sub>x</sub>Te<sub>1-x</sub> deposition rate at varied alloyed source compositions) to better understand which defect(s) can turn CdSe<sub>x</sub>Te<sub>1-x</sub> n-type and which defects, if any, remain in GrV-doped films. It would be enlightening to repeat density functional theory modeling<sup>[68]</sup> with the inclusion of Cl, Se, and GrV dopants.

## 4. Conclusion

Se alloying of CdTe solar cells may present a double-edged sword where the density of deep non-radiative defects is reduced on one hand, but shallower, radiative donor defects are introduced on the other, which can turn the  $\rm CdSe_xTe_{1.x}$  n-type (with electron density on the order of  $10^{16}~\rm cm^{-3}$ ) and limit  $V_{OC}$ . Losses associated with n-type  $\rm CdSe_xTe_{1.x}$  (e.g., buried junction effects, compensation, low activation) may be amplified in highly-doped GrV devices, which theoretical studies show are more sensitive to the front interface than low-doped Cu devices. Additionally,  $\rm CdSe_{0.3}Te_{0.7}$  (the composition used in champion NREL-grown devices) treated with GrV-optimized  $\rm CdCl_2$  conditions demonstrated increased nonradiative recombination, which may be one of the reasons GrV-doped devices can have lower lifetimes than Cu-doped devices.

Preferential loss of Se, as evidenced in the "slow deposition" sample which was evaporated from an alloyed  $CdSe_{0.3}Te_{0.7}$  source but measured CdSe<sub>0.23</sub>Te<sub>0.77</sub> in the final film, along with recent theoretical work suggests anion vacancies may be generated more readily in CdSe<sub>x</sub>Te<sub>1-x</sub> than CdTe. This may lead to a much higher density of anion vacancies, particularly during the CdCl<sub>2</sub> anneal, which is the main driver for Se diffusion. This would then create optimal conditions for chlorine doping of CdSe, Te<sub>1,x</sub> (e.g., Cl<sub>Te</sub> formation), which is of concern in GrV-doped devices since dopants and Cl would compete for the same sites. This may be a reason that CdSe<sub>x</sub>Te<sub>1-x</sub> is harder to dope p-type than CdTe. Importantly, this work suggests defect generation during the CdCl<sub>2</sub> anneal may be more harmful than defects generated during CdSe, Te<sub>1,y</sub> deposition (e.g., anion vacancies in either case), meaning it may be more impactful to maintain a Se overpressure during the former. DLTS showed a band of defects, which may include defects that interact to form complexes.

Finally, the uniform n-type behavior shown throughout the films here suggests that spatial non-uniformities in electrical properties seen in graded samples, are not inherent in  $CdSe_xTe_{1-x}$ , but are likely driven by differences in composition within the stack, so deposition from an alloyed source may be preferential.

Understanding the conditions at which  $CdSe_xTe_{1-x}$  becomes n-type and controlling/accounting for this behavior may help in realizing the full potential of Se alloying, both in standard p-type CdTe architectures and potentially for highly doped n-type  $CdSe_xTe_{1-x}$ -only devices.

### 5. Experimental Section

Sample Preparation: CdSe $_x$ Te $_{1\cdot x}$  test structures were fabricated on TEC12D, a commercial soda-lime glass substrate coated with a conductive SnO $_2$  layer. TEC12D substrates were used rather than uncoated glass (e.g., Eagle XG) to keep the structure of the CdSe $_x$ Te $_{1\cdot x}$  (e.g., grain morphology, size, crystallinity) as similar to devices as possible. Test structure architecture varied slightly based on the characterization method. For TRPL and PL characterization, CdSe $_x$ Te $_{1\cdot x}$  double heterostructures were fabricated by first depositing 100 nm of Al $_2$ O $_3$  on the TEC12D surface via electron beam evaporation with no intentional heating of the substrate (pressure  $\approx$ mid 10 $^{-6}$  Torr, 2 Å/sec deposition rate). The 3  $\mu$ m of uniform-composition CdSe $_x$ Te $_{1\cdot x}$  was then thermally evaporated from a ternary source powder (x = 0, 0.1, 0.2, 0.3, 0.4) at substrate temperature (T $_{sub}$ ) = 450 °C. Typically, a deposition rate of 16 Å s $^{-1}$  was maintained, except in the case that the deposition rate was intentionally decreased to 2 Å s $^{-1}$  ("slow deposition" CdSe $_{0.3}$ Te $_{0.7}$ ).

Film stacks were then annealed in a  $CdCl_2$ -rich ambient in a close-space sublimation configuration with no Se overpressure. In most cases, the source material ( $CdCl_2$  beads) was held at  $T_{source} = 495\,^{\circ}\text{C}$  and  $T_{sub} = 500\,^{\circ}\text{C}$  for 10 min in 400 Torr He. In one case,  $CdSe_{0.3}Te_{0.7}$  was annealed at  $T_{sub} = 500\,^{\circ}\text{C}$  with other conditions changed to what is commonly used for NREL-grown GrV devices (labeled "GrV-optimized  $CdCl_2$ " in this work). Because this process uses proprietary conditions, they are not detailed here. After  $CdCl_2$  treatment,  $CdSe_xTe_{1-x}$  films were briefly rinsed in DI water, as is done in NREL-grown devices. For PL and TRPL measurements, 20 nm of  $Al_2O_3$  was evaporated (same conditions as above) followed by a second, lower-temperature  $CdCl_2$  anneal ( $T_{sub} = 400\,^{\circ}\text{C}$ , 400 Torr He, 10 min). The wide bandgap  $Al_2O_3$  layers that sandwich the  $CdSe_xTe_{1-x}$  are thought to provide field-effect passivation and possibly also chemical passivation.[52]

For DLTS and SSRM measurements,  $CdSe_{0.3}Te_{0.7}$  was grown directly on TEC12D rather than Al<sub>2</sub>O<sub>3</sub>-coated TEC12D. CdCl<sub>2</sub> was done as described above and 100 nm of Au was thermally evaporated on the back. A small amount of film stack was then scraped away to reveal the front contact. For SSRM measurements, these film stacks were thermo-mechanically cleaved at the  $SnO_2/CdSe_xTe_{1-x}$  interface using a process similar to that described by Perkins et al. [54] Briefly, an Al shim handle was epoxied to the CdSe<sub>x</sub>Te<sub>1-x</sub> back surface with a conductive Ag-filled epoxy (Epo-tek H20E) and annealed in an oven overnight at 80 °C. These stacks were then dipped into liquid nitrogen (LN2) within an Ar-filled glovebox until spontaneous cleavage occurred. For AES and Hall, CdCl<sub>2</sub>-treated CdSe<sub>x</sub>Te<sub>1-x</sub> films grown on Al<sub>2</sub>O<sub>3</sub>-coated TEC12D (no back surface layers) were cleaved using the same process, where samples for Hall were cleaved using an insulating epoxy (Hysol 1C). After cleavage, the CdSe<sub>x</sub>Te<sub>1-x</sub> side of the cleave was extracted from the LN<sub>2</sub> bath into a stream of dry N<sub>2</sub> until room temperature was reached. Samples were then transferred without air exposure into the respective characterization tool for measurement.

Characterization: TRPL measurements were taken on a home-built system described elsewhere.  $^{[41]}$  A diode laser with 670 nm wavelength excitation and 50  $\mu m$  beam diameter was used at a repetition rate of 125 kHz. Laser power measured at the sample was 0.11  $\mu W$ , giving a fluence of  $\sim\!2\times10^{11}$  cm $^{-2}$  and injection level of  $\sim\!8\times10^{15}$  cm $^{-3}$  assuming a generation depth of 200 nm for 670 nm excitation in CdSe $_{0.3}$ Te $_{0.7}$ .  $^{[41]}$  A longpass filter of 700 nm ( $\sim\!1.77$  eV) was placed in the optical path before the Si avalanche photodiode detector.

PL measurements were taken using 632.8 nm excitation with a HeNe laser of beam diameter 0.9 mm at 1 Sun equivalent excitation (2  $\times$   $10^{21}$  photons/(m²s)). A pairing of spectrally corrected Si and InGaAs detectors (PIX100F Si CCD and Pylon IR, respectively) was used to obtain a larger

SCIENCE

www.advancedscience.com

spectral range (Si sensitive up to  $\approx$ 960 nm, InGaAs sensitive at longer wavelengths, see Figure S10, Supporting Information). Detectors were calibrated using an IntelliCal intensity calibration system (Princeton Instruments). A comparison with absolute reflectance standards (LabSphere) was used to measure PL emission spectra in absolute photon numbers.

Prior to AES,  $CdSe_xTe_{1-x}$  films were thermo-mechanically cleaved from their TEC12D substrates using the process described above. To better understand bulk composition, exposed films were first sputtered with a 2 kV ion beam at 70° angle measured from the surface normal and while rotating at 1 rpm. AES sensitivity factors were calculated as described previously<sup>[69]</sup> using sputter depth profile data on an ungraded  $CdSe_{0.08}Te_{0.92}$  film whose composition had been determined by X-ray fluorescence. AES measurements were done using a 5 kV, 20 nA beam. The spectrometer binding energy scale was calibrated at high and low energy using clean gold and copper foils and known transition energies.<sup>[70]</sup> Data analysis and peak fitting were performed using a combination of Igor and PHI MultiPak.

DLTS data were collected using a SULA Technologies digital model DDS-12 DLTS system.  $^{[71]}$  This system uses a 1 MHz modulating signal. The samples were measured between 0.3 V reverse bias and 0 V. Capacitance transients were averaged with a 40 s time constant with temperature held steady during measurement of all transients in the designated time windows (2, 5, 10, 20, 50, and 100 ms).

SSRM was done using an AFM (Veeco D5000 and Nanoscope V) housed in an Ar-filled glovebox. During measurement, a highly doped (p-type) diamond-coated Si probe (Bruker-nano DDESP) is pressed into the sample with a large indentation force ( $\approx\mu$ N), and a large bias voltage ( $\approx$ 5 V) is applied at the back contact. The total resistance ( $R_{tot}$ ) measured is composed of the spreading resistance ( $R_s$ ) of the sample, contact resistance at the probe/sample interface ( $R_c$ ), and back-contact resistance ( $R_b$ ).  $R_b$  is much smaller than  $R_c$  and  $R_{sp}$  since current pathways are spread out when reaching the back contact and series resistance in the film is relatively low (typically only a few  $\Omega \cdot \text{cm}^2$ ). Thus, if contact resistance is minimized (by using a large indentation force and large forward bias voltage and maintaining an inert ambient to prevent sample oxidation), [22,72] the measured resistance is dominated by  $R_{sp}$ . For depth profiling, samples were bevel-polished from the back using plane-view ion-milling at a maximum glancing angle of 7°.

Hall measurements were done using an Accent HL5500PC system. Thermomechanical cleaving, as described above, results in films with irregularly shaped areas so prior to measurement, a square  $\approx 5 \times 5$  mm was cut through the film and epoxy. Indium contacts were placed in the corners and the van der Pauw technique was used. XRD measurements were made using a Rigaku DMAX X-ray diffractometer that was set up using Bragg-Brentano geometry. A Cu K $\alpha$  radiation source was used at 40 kV and 250 mA excitation, and samples were scanned from 20 to 140 degrees  $2\theta$ . Phase information and lattice parameters for CdSe $_x$ Te $_{1x}$  were extracted from the literature.  $[^{145}]$

Optical images were taken on  $CdCl_2$ -treated  $CdSe_xTe_{1.x}$  (no back surface layers) using a Zeiss M2m Imager with AxioVision software at 100x magnification. While a Benson etch[<sup>73</sup>] is typically required to increase the contrast between grain boundaries and interiors (GBs are preferentially etched), this was not required here. Average grain size was calculated using ImageJ software and standard E112-12 developed by the American Society for Testing and Materials (ASTM). [<sup>74</sup>]

# **Supporting Information**

Supporting Information is available from the Wiley Online Library or from the author.

# **Acknowledgements**

The authors would like to thank Craig L. Perkins for AES measurements, analysis, and valuable discussion. The authors also thank Eric Colegrove for valuable discussion regarding the interpretation of capacitance-based

measurements. This work was authored by the National Renewable Energy Laboratory, operated by Alliance for Sustainable Energy, LLC, for the U.S. Department of Energy (DOE) under Contract No. DE-AC36-08GO28308. Funding was provided by the U.S. Department of Energy Office of Energy Efficiency and Renewable Energy Solar Energy Technologies Office under Agreement No. 38257. The views expressed in the article do not necessarily represent the views of the DOE or the U.S. Government.

### **Conflict of Interest**

The authors declare no conflict of interest.

# **Data Availability Statement**

The data that support the findings of this study are available from the corresponding author upon reasonable request.

### **Keywords**

cadmium telluride, chlorine, defects, n-type, Se alloy

Received: November 29, 2023 Revised: April 5, 2024 Published online: June 3, 2024

- EIA. Construction cost data for electric generators installed in 2020.

EIA, https://www.eia.gov/electricity/generatorcosts/ (accessed: May 2023).

- [2] H. M. Wikoff, S. B. Reese, M. O. Reese, Joule 2022, 6, 1710.

- [3] R. Mallick, X. Li, C. Reich, X. Shan, W. Zhang, T. Nagle, L. Bok, E. Bicakci, N. Rosenblatt, D. Modi, IEEE J. Photovoltaics 2023, 13, 510.

- [4] N. R. E. Laboratory, Best Research-Cell Efficiency Chart. https://www.nrel.gov/pv/cell-efficiency.html (accessed: March 2024).

- [5] C. Hagenorf, M. Ebert, M. Raugei, D. Lincot, J. Bengoechea, M. C Rodriguez, Report: Assessment of Performance, Environmental, Health and Safety Aspects of First Solar's CdTe PV Technology, National Renewable Energy Centre (CENER), Navarre, Spain, 2016.

- [6] T. A. M. Fiducia, B. G. Mendis, K. Li, C. R. M. Grovenor, A. H. Munshi, K. Barth, W. S. Sampath, L. D. Wright, A. Abbas, J. W. Bowers, J. M. Walls, *Nat. Energy* 2019, 4, 504.

- [7] T. Ablekim, J. N. Duenow, C. L. Perkins, J. Moseley, X. Zheng, T. Bidaud, B. Frouin, S. Collin, M. O. Reese, M. Amarasinghe, Sol. RRL 2021. 5, 2100173.

- [8] M. Amarasinghe, D. Albin, D. Kuciauskas, J. Moseley, C. L. Perkins, W. K. Metzger, Appl. Phys. Lett. 2021, 118, 211102.

- [9] N. R. Paudel, Y. Yan, Appl. Phys. Lett. 2014, 105, 183510.

- [10] A. Shah, A. P. Nicholson, T. A. Fiducia, A. Abbas, R. Pandey, J. Liu, C. Grovenor, J. M. Walls, W. S. Sampath, A. H. Munshi, ACS Appl. Mater. Interfaces 2021, 13, 35086.

- [11] W. K. Metzger, S. Grover, D. Lu, E. Colegrove, J. Moseley, C. Perkins, X. Li, R. Mallick, W. Zhang, R. Malik, Nat. Energy 2019, 4, 837.

- [12] G. Kartopu, O. Oklobia, D. Turkay, D. Diercks, B. Gorman, V. Barrioz, S. Campbell, J. Major, M. K. Al Turkestani, S. Yerci, Sol. Energy Mater. Sol. Cells 2019, 194, 259.

- [13] B. E. McCandless, W. A. Buchanan, C. P. Thompson, G. Sriramagiri, R. J. Lovelett, J. Duenow, D. Albin, S. Jensen, E. Colegrove, J. Moseley, Sci. Rep. 2018, 8, 14519.

- [14] A. Kanevce, M. O. Reese, T. Barnes, S. Jensen, W. Metzger, J. Appl. Phys. 2017, 121, 214506.

- [15] R. Pandey, T. Shimpi, A. Munshi, J. R. Sites, IEEE J. Photovoltaics 2020, 10. 1918.

www.advancedscience.com

- [16] T. Ablekim, E. Colegrove, W. K. Metzger, ACS Appl. Energy Mater. 2018, 1, 5135.

- [17] A. Mannodi-Kanakkithodi, M. Y. Toriyama, F. G. Sen, M. J. Davis, R. F. Klie, M. K. Chan, npj Comput. Mater. 2020, 6, 1.

- [18] E. Colegrove, B. Good, A. Abbas, H. Moutinho, S. Johnston, C.-S. Jiang, P. O'Keefe, J. M. Walls, D. S. Albin, M. O. Reese, Sol. Energy Mater. Sol. Cells 2022, 246, 111886.

- [19] S. Seto, A. Tanaka, Y. Masa, M. Kawashima, J. Cryst. Growth 1992, 117, 271.

- [20] P. Höschl, R. Grill, J. Franc, P. Moravec, E. Belas, *Mater. Sci. Eng., B* 1993, 16, 215.

- [21] W. Wang, V. Palekis, M. Z. Alom, S. E. Tawsif, C. Ferekides, In 2022 IEEE 49th Photovoltaics Specialists Conference (PVSC), IEEE, New York, 2022, 0988–0990.

- [22] P. Eyben, F. Clemente, K. Vanstreels, G. Pourtois, T. Clarysse, E. Duriau, T. Hantschel, K. Sankaran, J. Mody, W. Vandervorst, J. Vac. Sci. Technol. B 2010, 28, 401.

- [23] D. Kuciauskas, M. Nardone, A. Bothwell, D. Albin, C. Reich, C. Lee, E. Colegrove, Advanced Energy Materials 2023, 13, 2301784.

- [24] C.-S. Jiang, D. Albin, M. Nardone, K. Howard, A. Danielson, A. Munshi, T. Shimpi, C. Xiao, H. R. Moutinho, M. M. Al-Jassim, Sol. Energy Mater. Sol. Cells 2022, 238, 111610.

- [25] D. K. Schroder, Semiconductor Material and Device Characterization, John Wiley & Sons, Hoboken, NJ, 2015.

- [26] J. Poortmans, V. Arkhipov, Thin Film Solar Cells: Fabrication, Characterization and Applications, John Wiley & Sons, Hoboken, NJ, 2006.

- [27] D. Lane, Sol. Energy Mater. Sol. Cells 2006, 90, 1169.

- [28] S. Collins, C. A. Hsu, V. Palekis, A. Abbas, M. Walls, C. Ferekides, In 2018 IEEE 7th World Conf. on Photovoltaic Energy Conversion (WCPEC) (A Joint Conf. of 45th IEEE PVSC, 28th PVSEC & 34th EU PVSEC), IEEE, New York, 2018, 0114–0118.

- [29] B. Frouin, T. Bidaud, S. Pirotta, T. Ablekim, J. Moseley, W. K. Metzger, S. Collin, APL Mater. 2024, 12, 031135.

- [30] T. Baines, L. Bowen, B. G. Mendis, J. D. Major, ACS Appl. Mater. Interfaces 2020, 12, 38070.

- [31] T. Ablekim, J. Duenow, C. Perkins, J. Moseley, X. Zheng, T. Bidaud, B. Frouin, S. Collin, M. Reese, M. Amarasinghe, Solar RRL 2021, 5, 2100173.

- [32] J. M. Kephart, A. Kindvall, D. Williams, D. Kuciauskas, P. Dippo, A. Munshi, W. Sampath, *IEEE J. Photovoltaics* 2018, 8, 587.

- [33] H. Tubota, Jpn. J. Appl. Phys. 1963, 2, 259.

- [34] V. Šnejdar, D. Berkova, J. Jerhot, Thin Solid Films 1972, 9, 97.

- [35] E. Wallin, T. Jarmar, U. Malm, M. Edoff, L. Stolt, *Thin Solid Films* 2011, 519, 7237.

- [36] B. Good, E. Colegrove, M. O. Reese, Sol. Energy Mater. Sol. Cells 2022, 246, 111928.

- [37] D. Kuciauskas, J. Moseley, P. Ščajev, D. Albin, *Rapid Res. Lett.* 2020, 14, 1900606.

- [38] A. Danielson, C. Reich, R. Pandey, A. Munshi, A. Onno, W. Weigand, D. Kuciauskas, S. Li, A. Bothwell, J. Guo, Sol. Energy Mater. Sol. Cells 2023, 251, 112110.

- [39] D. Kuciauskas, M. Nardone, A. Bothwell, D. Albin, C. Reich, C. Lee, E. Colegrove, Adv. Energy Mater. 2023, 13, 2301784.

- [40] D. L. McGott, C. P. Muzzillo, C. L. Perkins, J. J. Berry, K. Zhu, J. N. Duenow, E. Colegrove, C. A. Wolden, M. O. Reese, *Joule* 2021, 5, 1057.

- [41] D. L McGott, B. Good, B. Fluegel, J. N. Duenow, C. A. Wolden, M. O. Reese, *Journal of Photovoltaics* 2021, 12, 309.

- [42] C.-S. Jiang, I. Repins, L. Mansfield, M. Contreras, H. Moutinho, K. Ramanathan, R. Noufi, M. Al-Jassim, Appl. Phys. Lett. 2013, 102, 253905.

- [43] C.-S. Jiang, H. Moutinho, R. Dhere, M. Al-Jassim, *IEEE J. Photovoltaics* **2013**, *3*, 1383.

- [44] C. Li, Y. Wu, J. Poplawsky, T. J. Pennycook, N. Paudel, W. Yin, S. J. Haigh, M. P. Oxley, A. R. Lupini, M. Al-Jassim, S. J. Pennycook, Y. Yan, Phys. Rev. Lett. 2014, 112, 156103.

- [45] A. J. Strauss, J. Steininger, J. Electrochem. Soc. 1970, 117, 1420.

- [46] J. D. Poplawsky, W. Guo, N. Paudel, A. Ng, K. More, D. Leonard, Y. Yan, Nat. Commun. 2016, 7, 1.

- [47] A. Abudulimu, J. Kulicek, E. Bastola, A. B. Phillips, A. Patel, D. Pokhrel, M. K. Jamarkattel, M. J. Heben, B. Rezek, R. J. Ellingson, In 2022 IEEE 49th Photovoltaics Specialists Conference (PVSC), IEEE, New York, 2022, pp 1088–1090.

- [48] M. J. Watts, P. Hatton, R. Smith, T. Fiducia, A. Abbas, R. Greenhalgh, J. M. Walls, P. Goddard, Phys. Rev. Mater. 2021, 5, 035403.

- [49] W. Orellana, E. Menéndez-Proupin, M. A. Flores, Sci. Rep. 2019, 9, 9194.

- [50] T. Fiducia, A. Howkins, A. Abbas, B. Mendis, A. Munshi, K. Barth, W. Sampath, J. Walls, Sol. Energy Mater. Sol. Cells 2022, 238, 111595.

- [51] J. Guo, A. Mannodi-Kanakkithodi, F. G. Sen, E. Schwenker, E. S. Barnard, A. Munshi, W. Sampath, M. K. Y. Chan, R. F. Klie, Appl. Phys. Lett. 2019, 115, 153901.

- [52] C. L. Perkins, T. Ablekim, T. M. Barnes, D. Kuciauskas, K. G. Lynn, W. Nemeth, M. O. Reese, S. K. Swain, W. K. Metzger, *IEEE J. Photovoltaics* 2018, 8, 1858.

- [53] C. L. Perkins, D. L. McGott, M. O. Reese, W. K. Metzger, ACS Appl. Mater. Interfaces 2019, 11, 13003.

- [54] C. L. Perkins, C. Beall, M. O. Reese, T. M. Barnes, ACS Appl. Mater. Interfaces 2017, 9, 20561.

- [55] I. Sankin, D. Krasikov, Appl. Mater. Sci. 2019, 216, 1800887

- [56] A. Shah, R. Pandey, A. Nicholson, Z. Lustig, A. Abbas, A. Danielson, J. Walls, A. Munshi, W. Sampath, Sol. RRL 2021, 5, 2100523.

- [57] M. Berding, Phys. Rev. B 1999, 60, 8943.

- [58] K. J. Price, MRS Online Proc. Libr. 2000, 668, 1.

- [59] S.-H. Wei, S. Zhang, Phys. Rev. B 2002, 66, 155211.

- [60] E. Colegrove, X. Zheng, T. Ablekim, J. N. Duenow, C. L. Perkins, H. R. Moutinho, W. K. Metzger, J. Phys. D: Appl. Phys. 2020, 54, 025501.

- [61] T. A. Fiducia, B. G. Mendis, K. Li, C. R. Grovenor, A. H. Munshi, K. Barth, W. S. Sampath, L. D. Wright, A. Abbas, J. W. Bowers, *Nat. Energy* 2019, 4, 504.

- [62] S. Paul, S. Sohal, C. Swartz, D.-B. Li, S. S. Bista, C. R. Grice, Y. Yan, M. Holtz, J. V. Li, Solar Energy 2020, 211, 938.

- [63] S. A. Awadalla, A. W. Hunt, K. G. Lynn, H. Glass, C. Szeles, S.-H. Wei, Phys. Rev. B 2004, 69, 075210.

- [64] M. A. Flores, W. Orellana, Phys. Rev. B 2016, 93, 184103.

- [65] V. Valdna, MRS Online Proceedings Library (OPL), Cambridge University Press, Cambridge, England, 1999, 607.

- [66] D. Keeble, J. Major, L. Ravelli, W. Egger, K. Durose, Phys. Rev. B 2011, 84, 174122.

- [67] S. Lany, A. Zunger, J. Appl. Phys. 2006, 100, 113725.

- [68] D. Krasikov, D. Guo, S. Demtsu, I. Sankin, Sol. Energy Mater. Sol. Cells 2021, 224, 111012.

- [69] C. L. Perkins, B. Egaas, I. Repins, B. To, Appl. Surf. Sci. 2010, 257, 878.

- [70] J. F. Moulder, J. Chastain, Handbook of X-ray Photoelectron Spectroscopy: A Reference Book of Standard Spectra for Identification and Interpretation of XPS Data, Physical Electronics Division, Perkin-Elmer Corporation, Waltham, MA 1992.

- [71] S. Weiss, R. Kassing, Solid-State Electron. 1988, 31, 1733.

- [72] L. Zhang, K. Ohuchi, K. Adachi, K. Ishimaru, M. Takayanagi, A. Nishiyama, Appl. Phys. Lett. 2007, 90, 192103.

- [73] J. Benson, L. Bubulac, P. Smith, R. Jacobs, J. Markunas, M. Jaime-Vasquez, L. Almeida, A. Stoltz, P. Wijewarnasuriya, G. Brill, J. Electron. Mater. 2010, 39, 1080.

- [74] (ASTM), A. S. f. T. a. M. ASTM E112-13: Standard Test Methods for Determining Average Grain Size, 2021.